Granite River Labs (GRL)

Latest releases surrounding USB4® Version 2.0

With the release of the latest USB4® Version 2.0 specification on October 18, 2022, USB-IF has once again doubled USB's data rate. This latest release allows USB Type-C® cables and connectors to provide 80Gbps performance and DisplayPort 2.1 support, which will benefit higher performance monitors, storage devices, and USB-based hubs and docks. USB Type-C® cable and connector specification 2.2 and USB PD 3.1 specification 1.6 were also released on the same day to support higher data transmission performance.

The launch follows VESA Association's latest DisplayPort (DP) 2.1 specification release on October 17, 2022. In the same week, Intel also conducted a prototype demonstration of its next-generation Thunderbolt™ that is both consistent with USB4® Version 2.0 specification and can support 80Gbps.

Combining data and video has been possible since the launch of the USB4 specification in 2019, where transfer speeds were doubled to USB 20Gbps (10Gbps x2) and USB 40Gbps (20Gbps x2). Fast charging capabilities of up to 240W PD, also fully satisfies gaming demands for high resolution display and fast charging.

In response to the continuous acceleration of global high-performance computing (HPC) applications, the latest USB4® Version 2.0 specification provides ultra-high transfer speed of USB 80Gbps (40Gbps x2), allowing USB4 to maintain its lead against competitors and dominate the field of external interface applications.

This article will provide a comprehensive overview of the specifications and performance of USB4 by covering the following topics:

- Introduction to USB4 Gen4

- Comparing PAM3 vs. PAM4 vs. NRZ

- Defining Data Rate and Baud Rate

- Comparing Bit Error Rate BER vs. TER

- Why USB4 Gen4 uses PAM3

- Total Loss considerations

- Bit Error Rate considerations

- USB4 Gen4 bandwidth optimization

- Asymmetric Link support to increase bandwidth up to 120 Gbps

- USB3 Gen T support to optimize bandwidth utilization

What is USB4 Gen4?

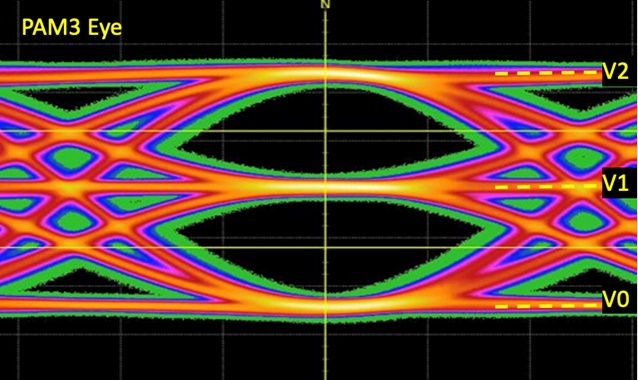

Figure 1. USB4 80Gbps PAM3 Eye Diagram

Denoted as USB4 Gen4, the newly released USB4 Version 2.0 specification has an electrical layer that taps into three voltage states for transmission in order to use Pulse Amplitude Modulation 3-level (PAM3) signal coding. This creates a two-eyed diagram as shown in Figure 1.

Each channel transmits at a Baud rate of 25.6GB, and the transmitter encodes binary bit signals in an 11-bits to 7-trits (ternary digit) mapping configuration to achieve a dual-channel 80Gbps transmission speed with PAM3 signals. Gen4 Link receivers require Trit Error Ratio (TER) of 1E-8 or lower without Forward Error Correction (FEC).

In addition to USB4 supporting USB3, DisplayPort, PCI Express (optional), and host-to-host tunneling, USB4 Version 2.0 further enhances the USB3 tunneling bandwidth utilization with the addition of a USB3 Gen T protocol adapter that in turn supports the latest DisplayPort 2.1. The new Asymmetric Link support further increases the bandwidth up to 120Gbps.

Defining common terms in the new PAM3 signal coding

PAM3 vs. PAM4 vs. NRZ

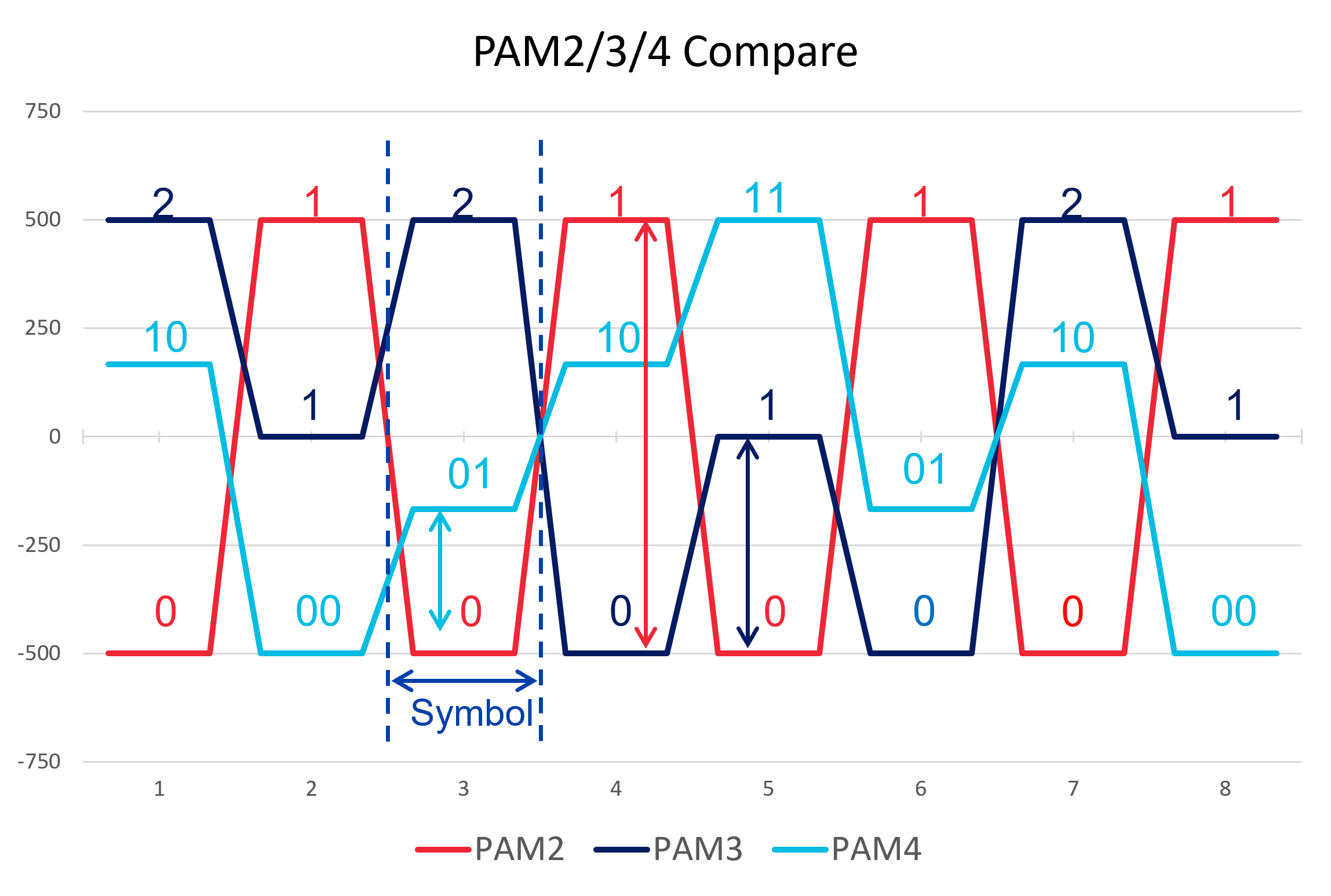

Figure 2. Comparison between PAM2, PAM3, and PAM4

Figure 2. Comparison between PAM2, PAM3, and PAM4

PAM3: Pulse Amplitude Modulation 3-level, ternary code, usually -1, 0, +1 or 0, 1, 2 to represent ternary values. Each PAM3 Symbol can transmit 1.58 bits (log2 3 = 1.58).

PAM4: Pulse Amplitude Modulation 4-level, usually represented by 00, 01, 10, 11. Each PAM4 symbol can transmit 2 bits per Symbol (log2 4 = 2).

NRZ, Non-Return-to-Zero, also known as Pulse Amplitude Modulation 2-level (PAM2), binary code, uses high and low level to represent logic 1 and 0. NRZ can transmit 1 bit per Symbol (log2 2 = 1).

Data Rate and Baud Rate

High-speed interface data rate is usually expressed in bps (bit per second). However, with the change in signal coding, such as Ethernet link transmitting with 50GBaud PAM4, data rate speeds can now go up to as high as 100Gbps.

Symbol Rate is expressed in Baud, where 1 Baud is the equivalent of one Symbol per second. The Data Rate is then calculated according to the number of bits carried by each Symbol under different coding mechanisms. The conversion relationship between the two follows this formula:

Data Rate = Baud Rate * Symbol carries the number of bits

- Under signal coding method NRZ, the Baud Rate will be equal to Data Rate, such as NRZ (PAM2) at 25.6 GBaud, the Data Rate is 25.6 Gbps (25.6 GBaud * log2 2).

- Under signal coding method PAM3, the Data Rate of PAM3 at 25.6 GBaud is 40.575 Gbps (25.6 GBaud * log2 3).

- USB4 Gen4 transmits at 25.6 GBaud speed with PAM3 signal, through 11-bits to 7-trits mapping, with a data rate of 40.2 Gbps (25.6 GBaud* 11/7), achieving 80Gbps with dual-lane transmission.

Note: PAM3 Symbol can carry a maximum of 1.58 bits (log2 3 = 1.58), and USB4 Gen4 has a Symbol carrying bit of 1.57 (11/7 bits), which utilizes 99% of the PAM3 transmission bandwidth.

Bit Error Rate BER vs. TER

Error rates in NRZ signals (transmitted in bits) are represented by BER (Bit Error Ratio). For ternary signal transmission of PAM3, the error rate is represented as TER (Trit Error Ratio) instead, where trit is an abbreviation for ternary digit.

Why USB4 Gen4 uses PAM3 over PAM4

For Gen4 to reach 80Gbps while using the same PCB and cable as Gen3, it must use the new signal coding of either PAM3 or PAM4 to meet the SI criteria with the following considerations:

PAM3 vs PAM4 total loss considerations

Signals are transmitted from the TX side of the host through the connector, cable, and then to the RX side of the device. The maximum allowable loss of the cable and PCB is the same as Gen3. If NRZ is used to transmit at 40Gbps, the transmission loss will exceed 40dB at the Nyquist frequency (20GHz). This amount of loss is too excessive for chipsets to compensate, resulting in an incorrect signal reflection that will show NRZ failing to meet Gen4 requirements. On the other hand, the total insertion loss for PAM4 and PAM3 at Gen4 Nyquist frequencies of 10GHz and 12.8GHz is approximately 23dB and 28dB respectively, a total loss amount that can still be compensated by the chipset and taken into consideration for analysis.

PAM3 vs PAM4 Bit Error Rate considerations

For receiver BER, the eye height of PAM3 is half that of NRZ while the eye height of PAM4 is 1/3 that of NRZ. This means that PAM3’s eye height and signal-to-noise distortion ratio (SNDR) are superior to those of PAM4. By conducting simulations and actual circuit experiments, it has been found that the uncoded BERs for PAM3 and PAM4 are 10E-8 and 10E-6 respectively. As such, PAM3 has been determined to be more compatible with USB4 Gen 4.

USB4 Gen4 bandwidth optimization

For USB4 Gen4 to reach 80Gbps while using the same PCB and cable as USB4 Gen3, new signal coding of either PAM3 or PAM4 must be used to meet the SI criteria with the following considerations:

- New Asymmetric Link operation to increase bandwidth up to 120 Gbps

- New USB3 Gen T for optimized bandwidth utilization

Asymmetric Link support to increase USB4 bandwidth up to 120 Gbps

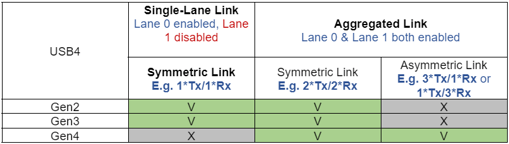

USB4 Links can be either Single-Lane Link or Aggregated Link, as shown in Table 1. In Single-Lane Link, only Lane 0 is enabled while Lane 1 is disabled. In Aggregated Link, both Lane 0 and Lane 1 are enabled and have a connection that is either symmetric or asymmetric.

Table 1. USB4 Symmetric Link and Asymmetric Link. The number of TX and RX lanes are the same in Symmetric Links, e.g. 1*TX/1*RX or 2*TX/2*RX

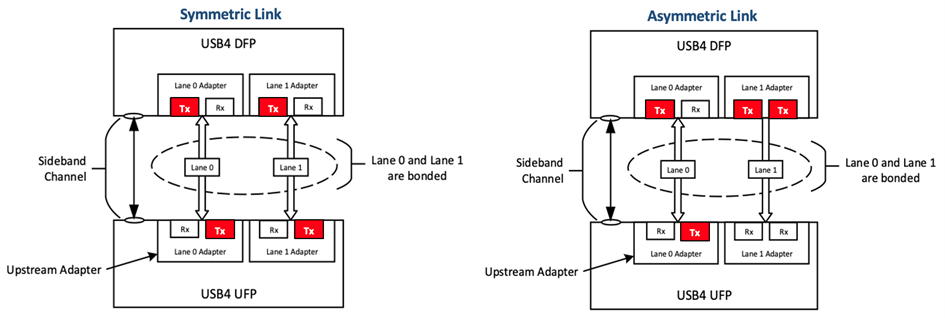

While USB4 Gen2 and Gen3 can only support Symmetric Link, Gen4 can also support Asymmetric Link. In an Asymmetric Link, one pair of TX/RX is used for DP transmission as TX/TX or RX/RX. This is illustrated in Figure 3, where one side transmits “3*TX/1*RX”, while the other side transmits “1*TX/3*RX”. This allows Gen4 to feature both high image resolution transmission DisplayPort 2.1 and high speed data transmission without reducing display quality. Transmissions of up to 120Gbps (40Gbps x3) in one direction can be enabled while maintaining a rate of 40Gbps in the opposite direction. Users may manipulate the Connection Manager to convert Symmetric Link to Asymmetric Links.

Figure 3. USB4 Symmetric Link and Asymmetric Link

USB3 Gen T support to optimize bandwidth utilization

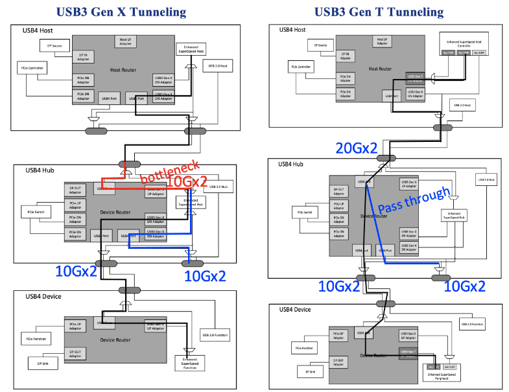

USB4 Version 2.0 saw the addition of support for USB3 Gen X and USB3 Gen T protocol tunneling, mainly to allow USB3 tunneling to make better use of USB4 transmission bandwidth.

- USB3 Gen X: USB3 tunnel architecture that uses the existing USB 3.2 protocol.

- USB3 Gen T: USB3 tunnel architecture that uses a modified USB 3.2 protocol to allow the use of the maximum bandwidth available for USB4.

To make sure that USB4 is backward compatible with USB3, the USB4 Gen2/Gen3 router must be equipped with a USB3 Protocol Adapter to encapsulate the native USB3 protocol data traffic and LFPS in the USB4 data package. The USB3 tunneling protocol that is currently used is represented as USB3 Gen X in USB4 Version 2.0 to differentiate it from the new USB3 Gen T.

Under the current USB3 Gen X tunneling protocol, the hub has only one Embedded SS Hub for uploading. As shown on the left-hand side of Figure 4, when the hub is connected to 2 devices (20Gbps) at its downstream ports for a total bandwidth of 40Gbps, the upstream bandwidth would still be limited to the embedded SS hub upstream maximum bandwidth of 20Gbps. This creates a bottleneck as the higher bandwidth of USB4 cannot be fully utilized.

Figure 4. Comparison between USB3 Gen X and USB3 Gen T Tunneling

The USB3 Gen T tunneling protocol uses a modified version of USB 3.2 protocol, which is mainly achieved by adding a USB3 Gen T protocol adapter. As shown on the right-hand side of Figure 4, the hub is connected to two devices, with both running at 20Gbps (USB3 10G x2). When both the host and devices support the USB3 Gen T, the hub upstream and downstream transmission will bypass the USB4 embedded SS hub. This allows the upstream bandwidth to reach 40Gbps as opposed to the 20Gbps bandwidth of the original USB3 Gen X. USB3 Gen T Tunneling is an optional support feature for host, hub, and device, which can more effectively utilize the bandwidth of USB4.

Conclusion

PAM3 signal coding allows the USB4 Gen4 data rates to reach new heights of 80Gbps. The bandwidth of USB4 Gen4 has been further optimized with the addition of Asymmetric Link support, which increases the bandwidth up to 120Gbps, and USB Gen T protocol adapter for optimized bandwidth utilization. While only 2 pairs of TX/RX need to be tested for signal quality, test complexity and duration will still have to increase to support Asymmetric Link, which requires all 4 pairs of TX/RX to be tested.

For designers and engineers, PAM3 signal coding presents new challenges. For one, SNDR will become a far more important consideration now that the NRZ eye height has been reduced to half of the original. Moreover, complex eye diagrams and jitter analysis will require much more time to understand.

Tap into extensive experience and deep expertise in USB compliance testing and certification at GRL, with test environments set up specifically for USB4 80Gbps.

Subscribe to our newsletter to receive the latest technical updates on USB4 Gen4 physical characteristics and PAM3 measurement and design considerations.

References:

- Universal Serial Bus 4 (USB4®) Specification, Version 2.0, October 2022

Author: Sandy Chang, Technical Director GRL Taiwan

- Experts in testing high-speed interfaces such as Thunderbolt™ 4, USB4™, USB3, DisplayPort, HDMI, PCI Express, etc.

Specifications and descriptions in this document can be subjected to changes by GRL without prior notice.

2022/10/20 AN-221020-EN