Granite River Labs, GRL

Wing Tseng 曾威華

DDR(Double Data Rate)の概要とメモリ改善効果とは?

この記事では、DDRの概要について、以下の流れで説明します:

- メモリのDRAMとSRAMへの分類

- SDRAMからDDR5への進化

- DDR4からDDR5への主なアップグレード

- DDRの5つの主な信号タイプ

- DDRとLPDDRの主な違い

DDR(Double Data Rate)を理解するためには、まず主要な3C製品(コンピュータ、通信、家電)におけるメモリの機能を理解することが重要です。メモリとは、デバイスの動作中にプログラムを安全に保管するための一時的なデータ記憶領域です。このストレージスペースにより、デバイスは保存された情報を迅速に取り出すことでプログラムを切り替えることができ、よりスムーズで効率的なユーザーエクスペリエンスを実現します。DDRテクノロジーは、データ転送速度の向上と電力効率の最適化によってデータ検索プロセスを改善し、2000年の誕生以来、現代のデバイスに広く採用されています。

DRAMとSRAMとは?

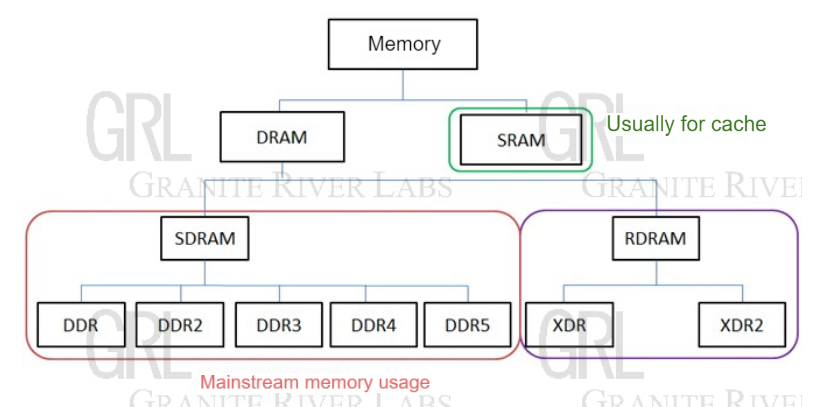

図1:DRAMとSRAMメモリのサブカテゴリーをさらにSDRAMとRDRAMの規格に分類した図

デバイスのストレージメモリは、大きく分けて2つのカテゴリーに分けられます: DRAM(Dynamic Random Access Memory)とSRAM(Static Random Access Memory)です。このほか、ラムバスDRAM(RDRAM)、高速ページモードRAM(FP RAM)、拡張データアウトRAM(EDO RAM)などがありますが、これらは普及が進んでおらず稀なメモリタイプだと考えられます。そのため、これらについて本稿では詳しく取り上げません。

DRAMもSRAMも揮発性メモリと言われ、データを保持するために一定の電力供給が必要です。DRAMがキャパシタやトランジスタを使用するのに対し、SRAMは主にフリップフロップを使用し、キャッシュに搭載されるのが一般的です。近年、DRAMの中でもSDRAM(Synchronous Dynamic Random Access Memory)と呼ばれるタイプのDRAMが最も多く使用されるようになりました。SDRAMはSingle Data Rate SDRAM(SDR SDRAM)とも呼ばれ、メモリクロックとCPUプロセッサを同期させることでSDRAMのブロック周波数が100MHzを超えることを可能にし、データ転送をよりリアルタイムに近づけます。

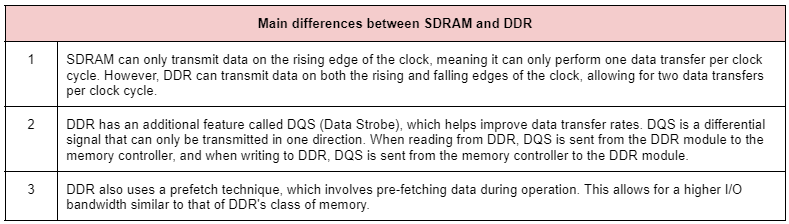

DDRとSDRAMの主な違いは、DDRがDDR SDRAMもしくはDouble Data Rate SDRAMの略であり、データ転送速度を2倍に高速化するために設計されたことから理解することができます。次の表は、2つのメモリ技術の技術的な違いをより詳細に説明したものです。:

表1:SDRAMとDDRの決定的な3つの違い

SDRAMからDDR5まで、DDR仕様の進化の歴史

DDRの仕様は、JEDEC Solid State Technology Associationとも呼ばれる、JEDEC(Joint Electron Device Engineering Council)が考案・策定しています。

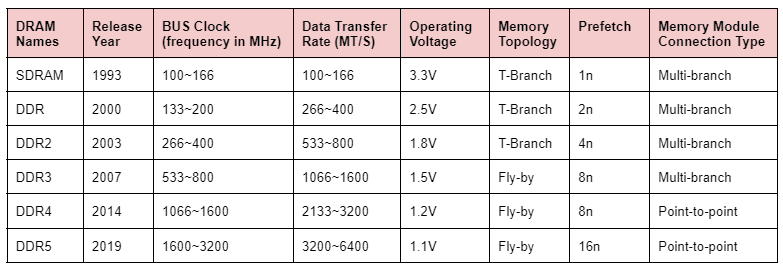

表2:歴代DDRの仕様

DRAMの仕様は、その歴史の中で、より高速な転送速度や低い動作電圧の実現に向けて進化してきました。DDR3では、DDR2以前のT分岐に代わり、コマンド/アドレス信号とクロック信号をより効率的に各メモリチップに伝達するフライバイ方式が採用されましたが、これは重要なマイルストーンとなりました。

もうひとつ画期的だったのは、DDR4で、CPUと複数のメモリチップコントローラーをつなぐ「マルチブランチ方式」のメモリ接続を、CPUとの「ポイント・トゥ・ポイント方式」の個別チャンネルに変更したことです。このダイレクトチャネル方式により、メモリアクセス効率の向上と消費電力の低減を実現し、システム性能の向上を実現しました。

DDR5がDDR4 RAMメモリをどのように改良したのか?

DDR5の開発により、より高密度で広帯域なメモリースティックの実現が期待され、3Cメーカーの間で大きな期待が寄せられています。DDR5では、メモリチップの容量を16ギガビットから64ギガビットに引き上げ、1チップに最大8個のダイを積み重ねることで、1モジュールあたり2TBの大容量化を実現します。

JEDECの規定するデータレート範囲はDDR5-3200までですが、DDR5の主流製品のデータレートはDDR5-4800くらいからが多いようです。これは、DDR4のデータレート範囲であるDDR4-1600からDDR4-3200に比べ、大幅に向上しています。また、DDR5メモリモジュールは、DDR4の64ビット1チャンネルに対し、独立した32ビット2チャンネルを搭載しています。

電力効率の面では、DDR5はDDR4の動作電圧である1.2Vを1.1Vまで下げています。本稿執筆時点では、すべての1.1VメモリキットがJEDECの指定タイミングに適合しています。

しかし、より多くのピンを導入したDDR4とは異なり、DDR5は依然として同じ288ピン配列にこだわっています。唯一の変更は、新しいユーザーが誤ってDDR4スロットにDDR5メモリモジュールを挿入したり、その逆を行うことを防ぐために、ノッチの位置を変更する異なるピンアウトにあります。

DDRの主な5つの信号タイプとは?

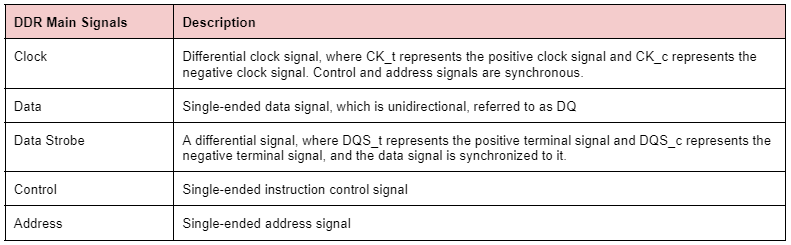

DDR信号は、メモリコントローラとモジュールの間でデータが正確かつ効率的に転送されるように連携して動作しています。クロック、データ、データストローブ、コントロール、アクセスの5つの主要なDDR信号は、データの保存、検索、転送、検証などにおいて相乗的な役割を果たします。次の表は、各信号の詳細について説明したものです。:

表3:主なDDR信号の種類についての説明

DDR は半二重動作で機能するように設計されており、読み出しと書き込みのメモリサイクルは、同じ信号トレース上で発生しますが、時間間隔が異なります。そのため、メーカーは正確なDDRテスト解析を行うために、読み出しサイクルと書き込みサイクルを区別することが重要です。

DDRの読み出しと書き込みサイクルは一致していないため、安定したHighまたはLowフェーズでデータ(DQ)を把握するためには、差動ストローブ信号(DQS)が必要です。DQとDQSは、読み出しサイクルでは同相で、書き込みサイクルでは90度の位相差があることに注意してください。

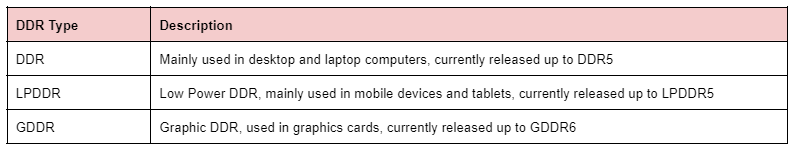

現在、DDRの種類は大きく分けて以下の3つに分類されます。:

表4:DDRの種類とカテゴリー

DDRとLPDDRの比較

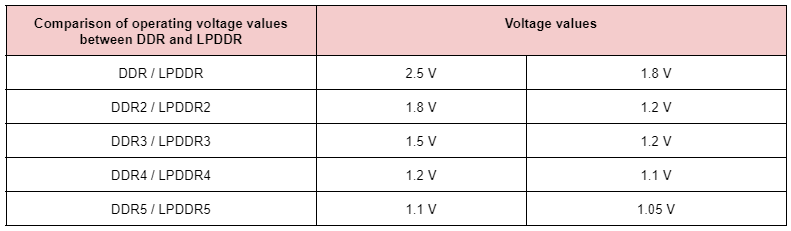

LPDDR は、スマートフォンやタブレットなどのモバイル機器向けに特別に設計された、低消費電力の同期型ダイナミックランダムアクセスメモリです。LPDDR は、性能、バッテリー寿命、したがってデータ転送の面で DDR と大きく異なります。

例えば、LPDDRを搭載したデバイスは、同等のDDRデバイスよりも消費電力が少なくなることが期待されます。その反面、同じベンチマークを使ったメモリテストでは、DDRデバイスの方がLPDDRデバイスより性能が良いことが考えられます。

そのため、搭載されるたびに進化してきたDDRとLPDDRの動作電圧値の違いを理解することが重要です。:

表5:DDRとLPDDRの動作電圧値

GRLによるDDR製品のテスト

製品開発のニーズに応じて、網羅的で信頼性の高いDDRコンプライアンス・テストをお探しですか?DDRからDDR5、LPDDRからLPDDR5までの仕様をカバーするDDRコンプライアンス・テスト・サービスをお探しなら、GRLの専門家が知識と設備を持って対応します。今すぐお問い合わせの上、専門的なコンサルテーションを受け、貴社の製品が最新の業界標準に適合していることを確認する方法をご確認ください。

参考文献

- Low Power Double Data Rate SDRAM Standard (LPDDR), JESD209B, February 2009

- Low Power Double Data Rate 2 (LPDDR2), JESD209-2F, April 2011

- DDR3 SDRAM Standard, JESD79-3F, July 2010

- Low Power Double Data Rate 3 (LPDDR3), JESD209-3C, August 2013

- DDR4 SDRAM, JESD79-4, September 2012

- Low Power Double Data Rate 4 (LPDDR4), JESD209-4B, November 2015

- Low Power Double Data Rate 5 (LPDDR5), JESD209-5, February 2019

- DDR5 SDRAM, JESD79-5, July 2020