Granite River Labs, GRL

Winson Mok

PCIe介面在日常工作和生活中無所不在,例如我們常見的電腦主機板、顯示卡、存儲類記憶體,甚至是無線網卡等消費性電子產品都有應用到PCIe介面。不知道大家有沒有發現,從PCIe 3.0到PCIe 4.0,更替時間長達7年之久,然而近來隨著電子產品、資料中心與人工智慧的快速發展和居高不下的需求,PCIe介面正快速發展著,運算能力一代比一代加強,目前PCIe 5.0已趨於成熟,PCIe 6.0則仍有一些標準(如CEM,PHY)尚在討論中,但PCI-SIG已經同步推進PCIe 7.0標準。

以上是PCIe標準的近期更新,以下內容則主要和大家交流PCIe 6.0技術的推進、一致性測試與運算能力。

從 PCIe 1.0 至 PCIe 6.0,PCIe 的高速演進

PCIe (Peripheral Component Interconnect Express) 是高速串行電腦匯流排標準,替代了原來的PCI,目前由PCI-SIG (PCI Special Interest Group) 負責制定和推廣標準,PCI-SIG自從2003年推出PCIe 1.0版本,至今不斷進化,2021發布了PCIe 6.0標準,傳輸能力從原本的2.5GT/s已經進化至64GT/s。

.jpg?width=1225&height=616&name=PCIe%201.0%E8%87%B3PCIe%206.0%E7%9A%84%E5%82%B3%E8%BC%B8%E9%A0%BB%E5%AF%AC%E8%AE%8A%E5%8C%96(%E4%BE%86%E6%BA%90PCI-SIG).jpg)

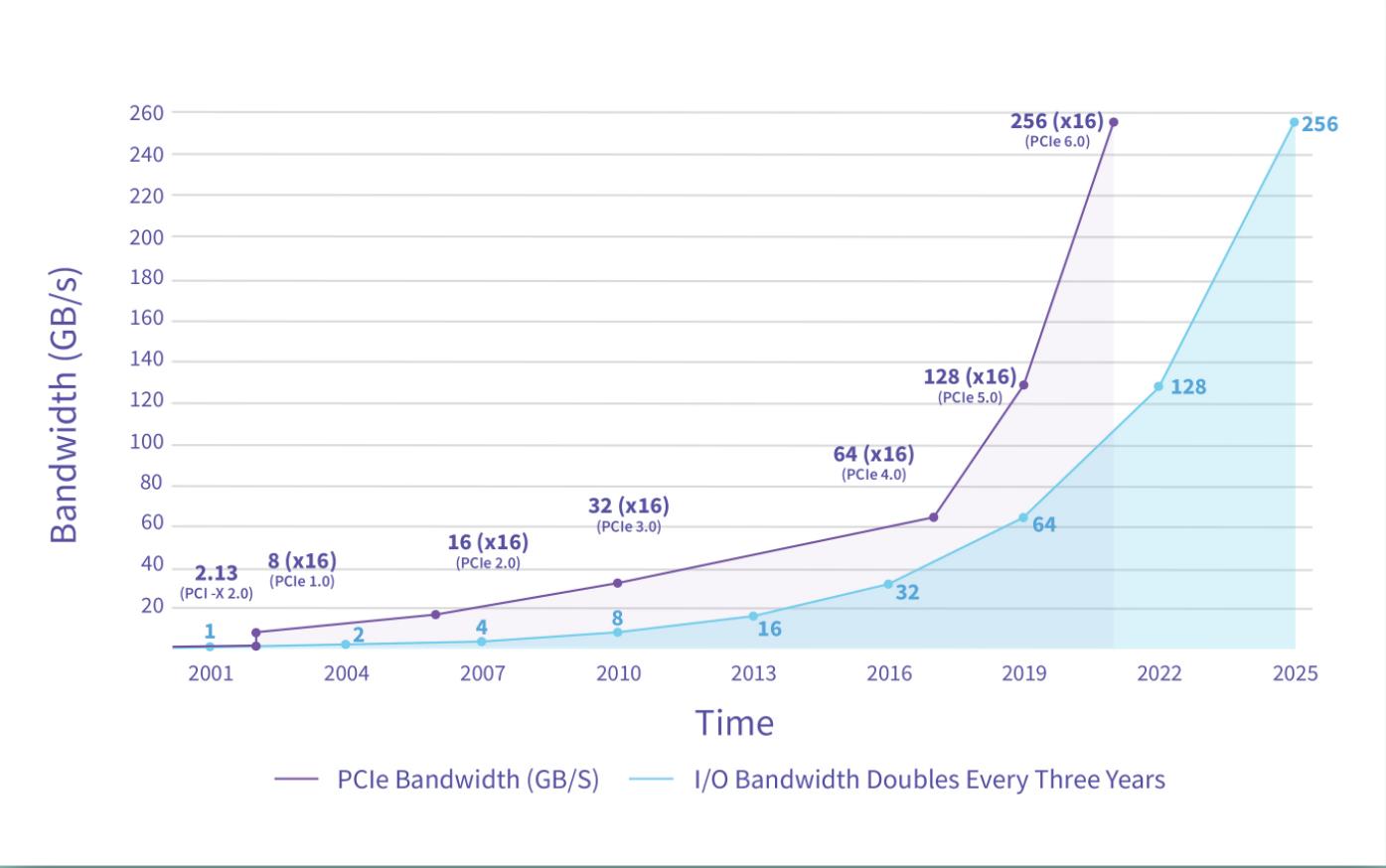

圖1: PCIe傳輸頻寬變化(來源:PCI-SIG)

圖2: PCIe傳輸容量變化(來源:PCI-SIG)

我們可以從圖1、圖2中得知PCIe介面的速率幾乎每一代都在翻倍成長,各個技術都在尋求「如何在傳輸頻寬保持不變的情況下,實現速率翻倍」的方法,PCIe 6.0也不例外。PCIe 6.0與前幾代標準相比,最大的變化就是訊號的編碼方式,PCIe 6.0以PAM4模式來傳輸,我們來簡單對照一下NRZ和PAM4訊號的區別。

不同於 NRZ 編碼,PCIe 6.0 採用 PAM4 編碼方式

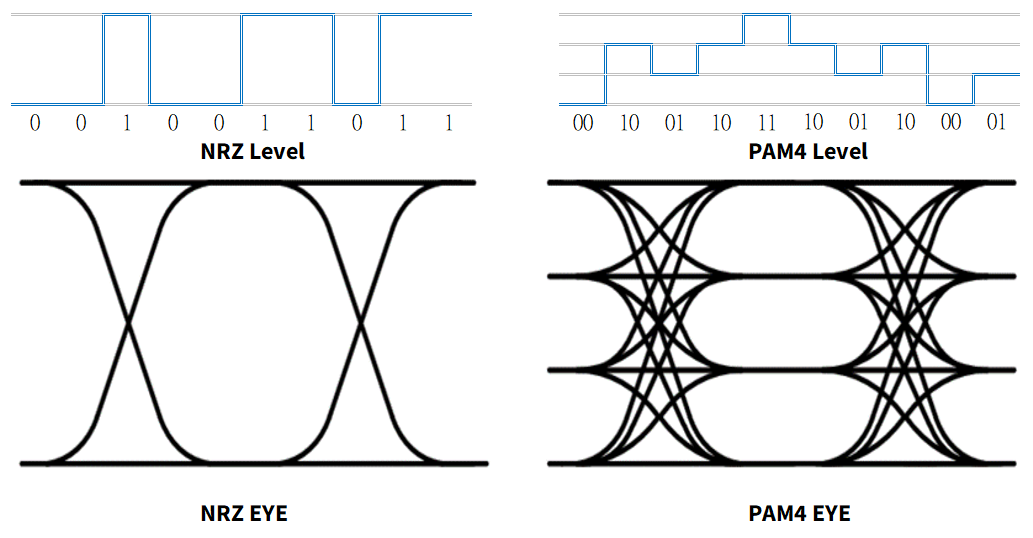

NRZ (Non-Return-to-Zero) 是一種不歸零的二進位訊號編碼模式,PCIe 1.0至PCIe 5.0都是採用這樣的編碼方式,然而為了提升傳輸速率,PCIe 6.0並沒有沿用NRZ編碼,而是採用了PAM4 (Pulse Amplitude Modulation 4-levels) 這種四階脈衝振幅調變的編碼方式;NRZ只用0、1兩個電平來形成一個眼圖,而PAM4會有0、1、2、3共4個電平,以形成3個眼圖。因此PAM4每個符號能攜帶2個bit的資訊,比NRZ每個符號只能攜帶1個bit資訊,傳輸能力提高了一倍,請參考圖3。

圖3: NRZ vs PAM4電平和眼圖

.jpg?width=1297&height=435&name=PAM4%E8%A8%8A%E8%99%9F%E7%9A%84UI%20Level(SourcePCIe%20Base%20Spec%20Revision%206.0.1).jpg)

圖4: PAM4訊號的UI Level(Source:PCIe Base Spec Revision 6.0.1)

PCIe 6.0採用PAM4編碼還有另一個優勢,就是即使傳輸64GT/s的速率,依然可以和PCIe 5.0的奈奎斯特頻率 (Nyquist Frequency) 保持一致,而通道IL從PCIe 5.0的36 dB變為了PCIe 6.0的32 dB,從另一個角度來看,PAM4還有助於降低通道的損耗。從圖4我們還可以得知,PAM4的4個電平 (Level 0,1,2,3) 進行格雷編碼 (Gray Coding),4個電平對應的格雷編碼分別是00、01、11、10,格雷編碼的方式是要求相鄰符號,每次只能變化一位元,且首尾符號也只是變化一位元,這樣的編碼方式可以有效改善誤碼率。並且PAM4訊號還定義了4個電平的直流平衡值 (DC Balance Values) 以滿足直流平衡設計需求。另外,雖然PCIe 6.0採用了PAM4編碼,但PCIe 6.0依然向下相容之前所有版本的速率。

PCIe 6.0 的特性與優勢

編碼方式的改變,讓PCIe 6.0的速率翻倍,擁有更高的傳輸效率,但由於PAM4有4個電平幅度,相比NRZ模式,每個眼睛 (Eye) 的幅度降低許多,所以訊號的傳輸過程中對雜訊更敏感,也更容易產生突發誤碼。這也給PCIe 6.0的訊號完整性帶來挑戰,要求更高的信噪比,而眼高的降低也代表著接收端需要有更高的靈敏度。

PCIe 6.0的特性:FBER (First Bit Error Rate)、FEC (Forward Error Correction) 機制與流量控制單元 (Flow Control Unit)

在PCIe 5.0的NRZ時代,BER (Bit Error Rate) 目標值要求是10-12。但在PCIe 6.0表徵誤碼率時會出現一個新的名詞FBER (First Bit Error Rate),規範FBER要求小於10-6,此處的FBER是沒有把任何的突發誤碼計算進去的。

對於高速率傳輸的訊號,特別是到了PAM4編碼時代,往往會出現比較高的誤碼率而無法達到規範要求,因此PCIe 6.0引進了FEC (Forward Error Correction) 前向錯誤更正機制,前向錯誤更正機制是訊號在發送端時就加入額外特定的冗餘資訊,當傳輸發生錯誤時,FEC機制可以在接收端把錯誤糾正過來以達到改善誤碼率的效果,另外,羽量級FEC還可以保持PCIe 6.0訊號傳輸的超低時間延遲。但值得注意的是,FEC的糾錯能力是有限的,如果發生大量錯誤,FEC也可能無法糾正。

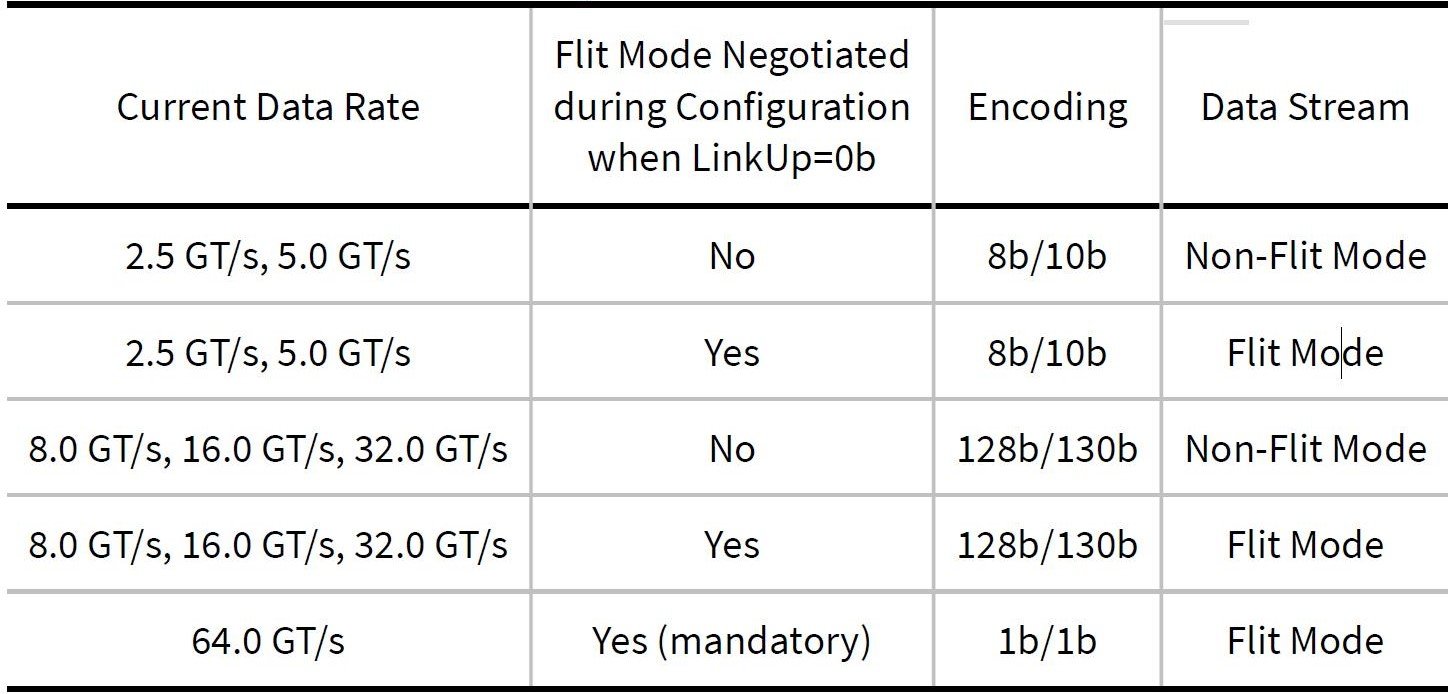

PCIe 6.0還具有流量控制單元 (Flow Control Unit) 模式,且是固定資料包大小 (Fixed Sized Code Words),相比之前版本的非Flit模式和編碼方式,PCIe 6.0要求強制使用Flit模式傳輸,編碼方式也改成了1b/1b,這就意味著傳輸的每一位元資訊都是有效碼,有別於以往8b/10b和128b/130b的傳統編碼。

另外,PCIe 6.0在能效方面也是優於PCIe 5.0的,PCIe 6.0具有全新的低功耗模式:L0p,它可以在保持數據傳輸的情況下靈活調節頻寬,以提高利用率,達到降低功耗目的,這對Server等級的產品來說是一個巨大的優勢。

圖5: 有效的編碼和資料流組合(來源:PCIe Base Spec Revision 6.0.1)

PCIe 6.0的均衡方面,依然保持發送端使用FFE,接收端使用CTLE和DFE組合的架構,但由於前面提到的PAM41編碼格式,每個眼睛(Eye)的幅度降低,使得電平間的幅度間隔變近了,所以可以看到PCIe 6.0的DFE從PCIe 5.0的3-Tap變為了16-Tap,以補償PAM4更容易產生碼間干擾問題。

GRL PCIe 6.0 自動化校正及測試解決方案

PCIe 6.0標準基本規範 (Base Specification) 目前已擬定完整,但Card Electromechanical (CEM) 規範和PHY測試規範還是處於0.5版本的狀態。

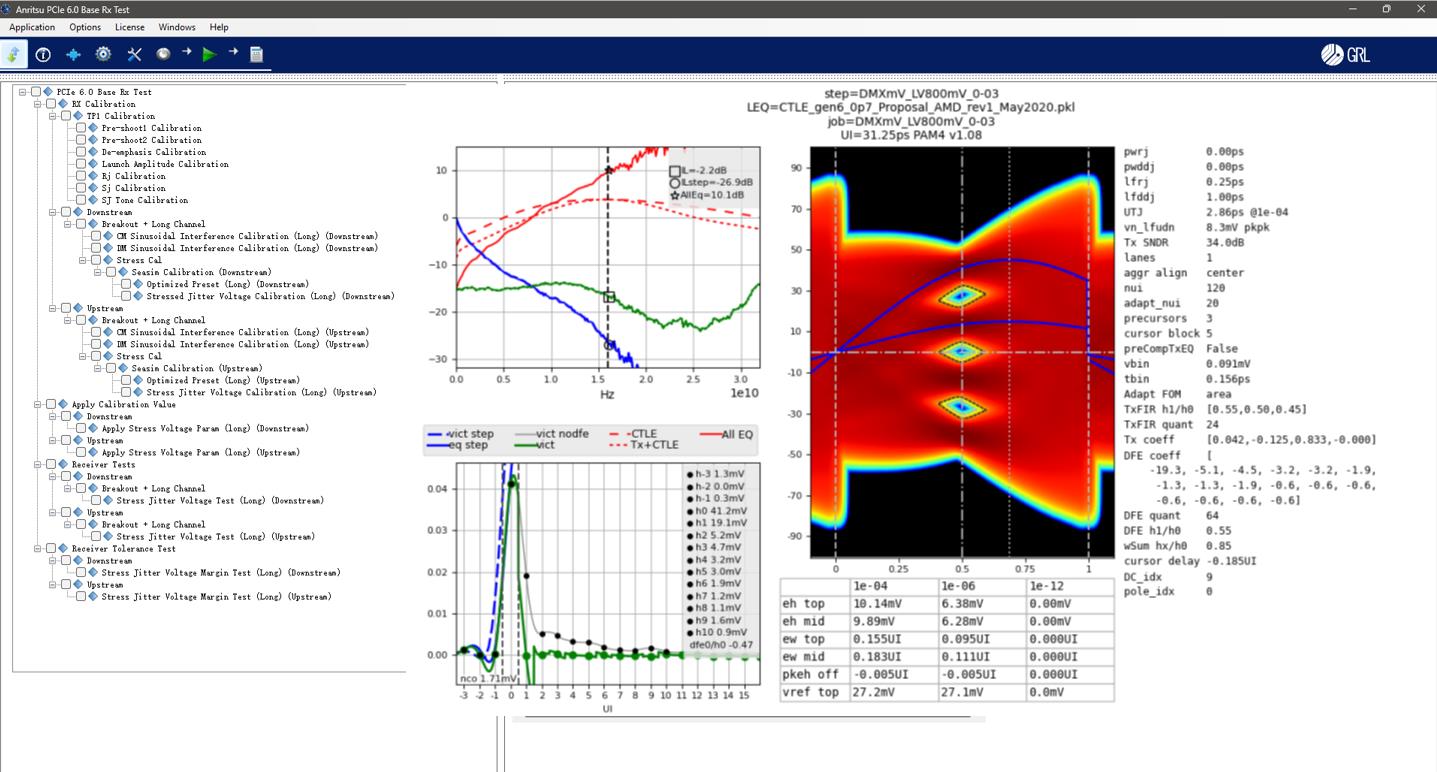

GRL緊隨PCI-SIG協會的腳步,不僅可以提供包括PCIe 5.0和前幾代的測試服務與解決方案,也針對PCIe 6.0推出了GRL-PCIE6-BASE-RXA自動化校正及測試解決方案。

圖6:GRL-PCIE6-BASE-RXA自動化校準及測試解決方案

結論

以上內容介紹了PCIe 6.0的PAM4編碼方式及相關特性 (FBER、FEC、Flow Control Unit)。相信PCIe 6.0將會給使用者帶來極致的體驗,同時也會為生產、研發部門帶來不一樣的挑戰;依照過去的經驗,應該不久後就能陸續看到PCIe 6.0產品有一致性測試的需求,GRL也會緊隨協會開發新標準的步伐,跟上PCIe的高速發展,繼續為客戶提供先進、全面的測試服務與測試解決方案,提供更好的一站式服務體驗。

參考文獻

- PCI-SIG, PCI Express® Base Specification Revision 6.0.1

- Advancing Artificial Intelligence and Machine Learning Applications, Vamshi Kandalla, Granite River Labs

作者

GRL東莞測試工程師 莫坤龍 Winson Mok

GRL測試工程師,在訊號完整性和存儲測試擁有多年的工作經驗,熟悉Thunderbolt、PCI Express、USB及Ethernet等多種測試規格,目前負責GRL東莞Storage的測試。

本文件中規格特性及其說明若有修改恕不另行通知。

發佈日期 2023/02/09 AN-230209-TW

.webp)

/PCIe%204.0%20Compliance%20Test_featured%20image.jpeg)

/PCIe%20Gen1234_featured%20image.jpeg)