Granite River Labs, GRL

Winson Mok

PCIe 인터페이스는 일상 업무와 생활에서 어디에나 있습니다. 예를 들어, 공통 컴퓨터 마더보드, 디스플레이 카드, 스토리지 메모리, 심지어 무선 네트워크 카드와 같은 소비자 전자 제품도 모두 PCIe 인터페이스에 적용됩니다. PCIe 3.0에서 PCIe 4.0으로 교체하는 데 걸린 시간이 무려 7년이라는 사실을 눈치채셨는지 모르겠습니다. 최근 전자제품과 데이터센터, 인공지능의 급속한 발전과 높은 수요로 PCIe는 인터페이스는 급속도로 발전하고 있으며 그 결과 컴퓨팅 파워는 세대를 거듭할수록 향상되어 현재 PCIe 5.0은 성숙기에 접어들었고 PCIe 6.0은 여전히 논의 중인 일부 표준(예: CEM, PHY)이 있지만 PCI- SIG는 동시에 PCIe 7.0 표준을 홍보했습니다.

위의 내용은 PCIe 표준의 최근 업데이트이며 다음 내용은 주로 PCIe 6.0 기술, 컴플라이언스 테스트 및 컴퓨팅 기능의 발전에 대해 설명합니다.

PCIe 1.0에서 PCIe 6.0으로, PCIe의 고속 진화

PCIe(Peripheral Component Interconnect Express)는 원래 PCI를 대체하는 high-speed serial computer bus 표준입니다. 현재 PCI-SIG(PCI Special Interest Group)에서 표준 공식화 및 홍보를 담당하고 있습니다. PCI-SIG는 2003년 PCIe 1.0 버전을 출시한 이후 지금까지 계속 진화해왔고 2021년에는 PCIe 6.0 규격이 나오며 전송 용량은 기존 2.5GT/s에서 64GT/s로 진화했습니다.

.jpg?width=1225&height=616&name=PCIe%201.0%E8%87%B3PCIe%206.0%E7%9A%84%E5%82%B3%E8%BC%B8%E9%A0%BB%E5%AF%AC%E8%AE%8A%E5%8C%96(%E4%BE%86%E6%BA%90PCI-SIG).jpg)

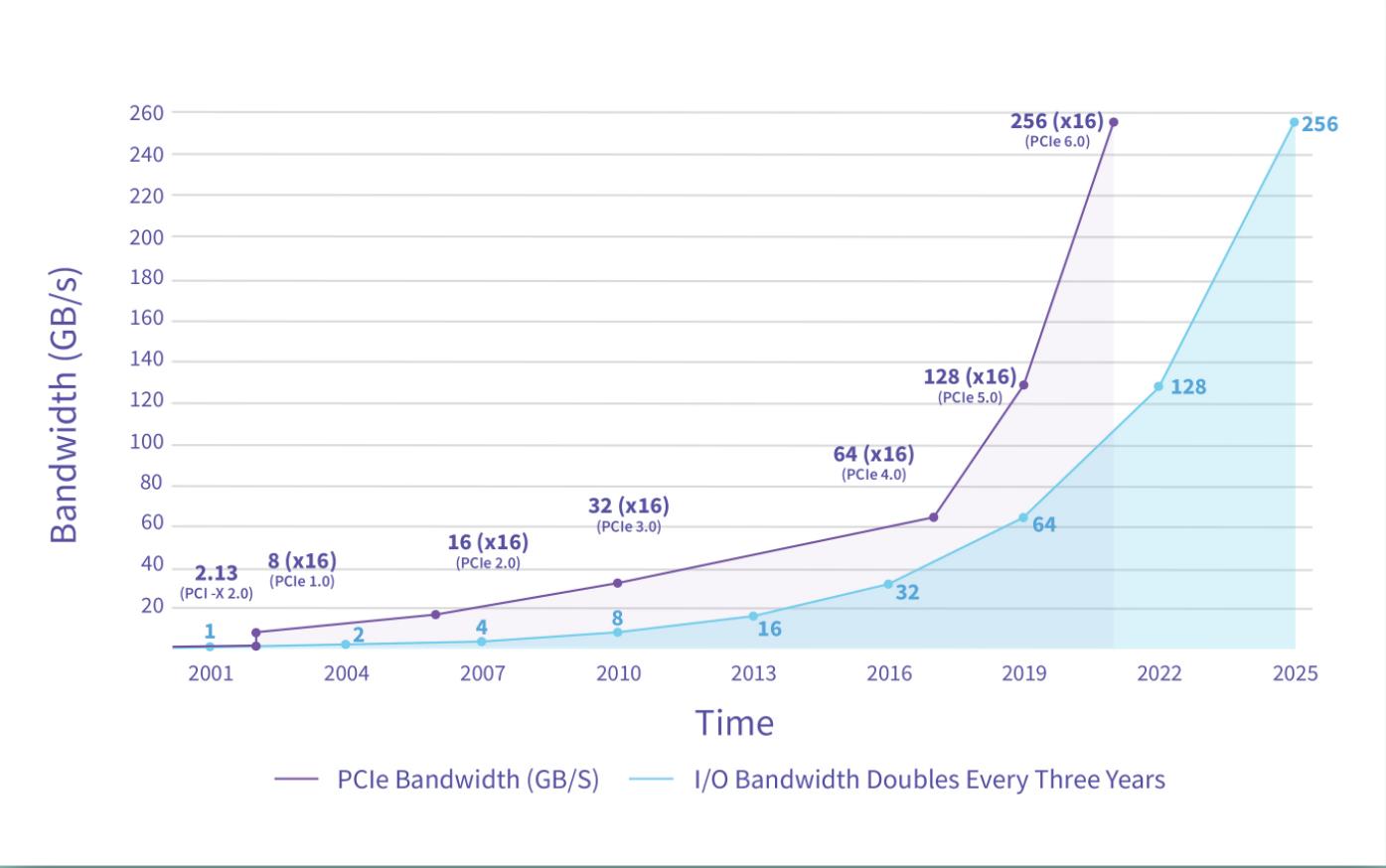

그림 1: PCIe 전송 대역폭의 변화(출처: PCI-SIG)

그림 2: PCIe 전송 용량의 변화(출처: PCI-SIG)

우리는 그림 1과 그림 2에서 PCIe 인터페이스의 속도가 거의 모든 세대에서 두 배로 증가하고 있으며 각 기술은 "동일한 전송 대역폭을 유지하면서 속도를 두 배로 늘리는 방법"을 모색하고 있음을 알 수 있습니다. PCIe 6.0도 예외는 아닙니다. 이전 세대의 표준과 비교할 때 PCIe 6.0의 가장 큰 변화는 신호 인코딩 방식입니다. PCIe 6.0은 PAM4 모드로 전송됩니다. NRZ와 PAM4 신호의 차이점을 간단히 비교해 보겠습니다.

NRZ 인코딩과 달리 PCIe 6.0은 PAM4 인코딩을 사용합니다.

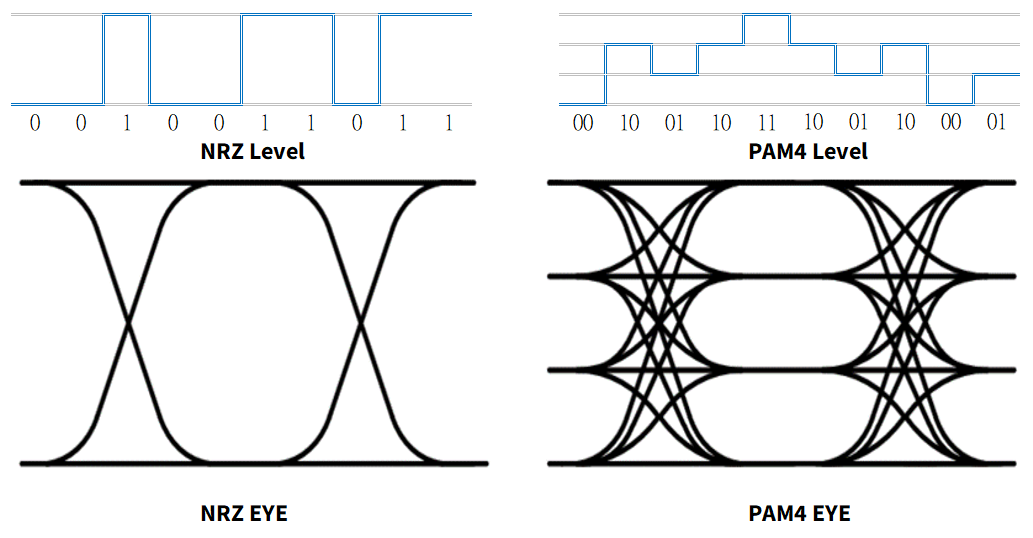

NRZ(Non-Return-to-Zero)는 0이 아닌 이진 신호 인코딩 모드입니다. PCIe 1.0부터 PCIe 5.0까지 모두 이 인코딩 방식을 채택합니다. 그러나 PCIe 6.0은 전송률을 높이기 위해 NRZ 인코딩을 사용하지 않고 4차 펄스 진폭 변조의 PAM4(Pulse Amplitude Modulation 4-levels) 인코딩 방식을 채택하고 있으며, NRZ는 0과 1의 두 가지 레벨만을 사용하여 아이 다이어그램을 형성하는 반면, PAM4는 총 4개 레벨을 사용하여 3개의 아이 다이어그램을 형성하게 됩니. 따라서 PAM4의 각 기호는 NRZ와 비교하여 2비트의 정보를 전달할 수 있고, 각 기호는 1비트의 정보만 전달할 수 있으며, 전송 용량은 두 배가 됩니다. 그림 3을 참조하십시오.

그림 3: NRZ 대 PAM4 레벨 및 아이 다이어그램

.jpg?width=1297&height=435&name=PAM4%E8%A8%8A%E8%99%9F%E7%9A%84UI%20Level(SourcePCIe%20Base%20Spec%20Revision%206.0.1).jpg)

그림 4: PAM4 신호의 UI 수준(출처: PCIe Base Spec Revision 6.0.1)

PAM4 인코딩을 사용하는 PCIe 6.0의 또 다른 장점은 전송 속도가 64GT/s이더라도 여전히 PCIe 5.0의 나이퀴스트 주파수(Nyquist Frequency)와 일치할 수 있으며 채널 IL이 PCIe 5.0의 36dB에서 PCIe로 변경된다는 것입니다. 6.0의 32dB, 또 다른 관점에서 PAM4는 채널 손실을 줄이는 데도 도움이 됩니다. 그림 4에서 PAM4의 4개 레벨(Level 0, 1, 2, 3)이 Gray Coded(Gray Coding)이며, 4개 레벨에 해당하는 Gray 코드가 각각 00, 01, 11, 10임을 알 수 있습니다. , 그레이 코딩 방법은 인접 심볼이 한 번에 한 비트만 변경하고 첫 번째 및 마지막 심볼은 한 비트만 변경하면 되므로 이 코딩 방법은 비트 오류율을 효과적으로 개선할 수 있습니다. 또한 PAM4 신호는 DC 밸런스 설계의 요구 사항을 충족하기 위해 4레벨의 DC 밸런스 값(DC Balance Values)을 정의합니다. 또한 PCIe 6.0은 PAM4 인코딩을 사용하지만 PCIe 6.0은 여전히 모든 이전 버전의 속도와 하위 호환됩니다.

PCIe 6.0의 기능 및 이점

코딩 방식의 변화로 PCIe 6.0보다 속도가 2배 빨라지고 전송 효율도 높아졌습니다. 그러나 PAM4는 4레벨 진폭을 가지므로 NRZ 모드에 비해 각 눈(Eye)의 진폭이 훨씬 낮아 신호 전송 과정 노이즈에 더 민감하고 버스트 비트 오류가 발생하기 쉽습니다. 이것은 또한 PCIe 6.0의 신호 무결성에 문제를 일으켜 더 높은 신호 대 잡음비를 요구하며 아이 높이의 감소는 수신기가 더 높은 감도를 가져야 함을 의미합니다.

PCIe 6.0의 기능: FBER(First Bit Error Rate), FEC(Forward Error Correction) 메커니즘 및 흐름 제어 장치(Flow Control Unit)

PCIe 5.0의 NRZ 시대에는 BER(Bit Error Rate)의 목표값이 10 -12가 되어야 하지만 PCIe 6.0이 비트 오류율을 특성화할 때 새로운 용어인 FBER(First Bit Error Rate)가 나타날 것 입니다. 표준 FBER 요구사항은 10-6 미만이며, 여기서 FBER에는 버스트 오류율이 포함되지 않습니다.

고속 전송 신호의 경우, 특히 PAM4 인코딩 시대에는 상대적으로 높은 비트 오류율이 자주 발생하고 사양 요구 사항을 충족하지 못하므로 PCIe 6.0은 FEC(Forward Error Correction) 순방향 오류 정정 메커니즘, 순방향 오류 정정을 도입합니다. 메커니즘은 송신단에서 신호에 특정 중복 정보를 추가하는 것입니다.전송에서 오류가 발생하면 FEC 메커니즘은 수신단에서 오류를 수정하여 비트 오류율을 향상시킬 수 있습니다.또한 featherweight FEC는 또한 PCIe 6.0 신호 전송을 위해 매우 낮은 대기 시간을 유지합니다. 그러나 FEC의 오류 수정 기능은 제한적이며 많은 수의 오류가 발생하면 FEC가 오류를 수정하지 못할 수 있습니다.

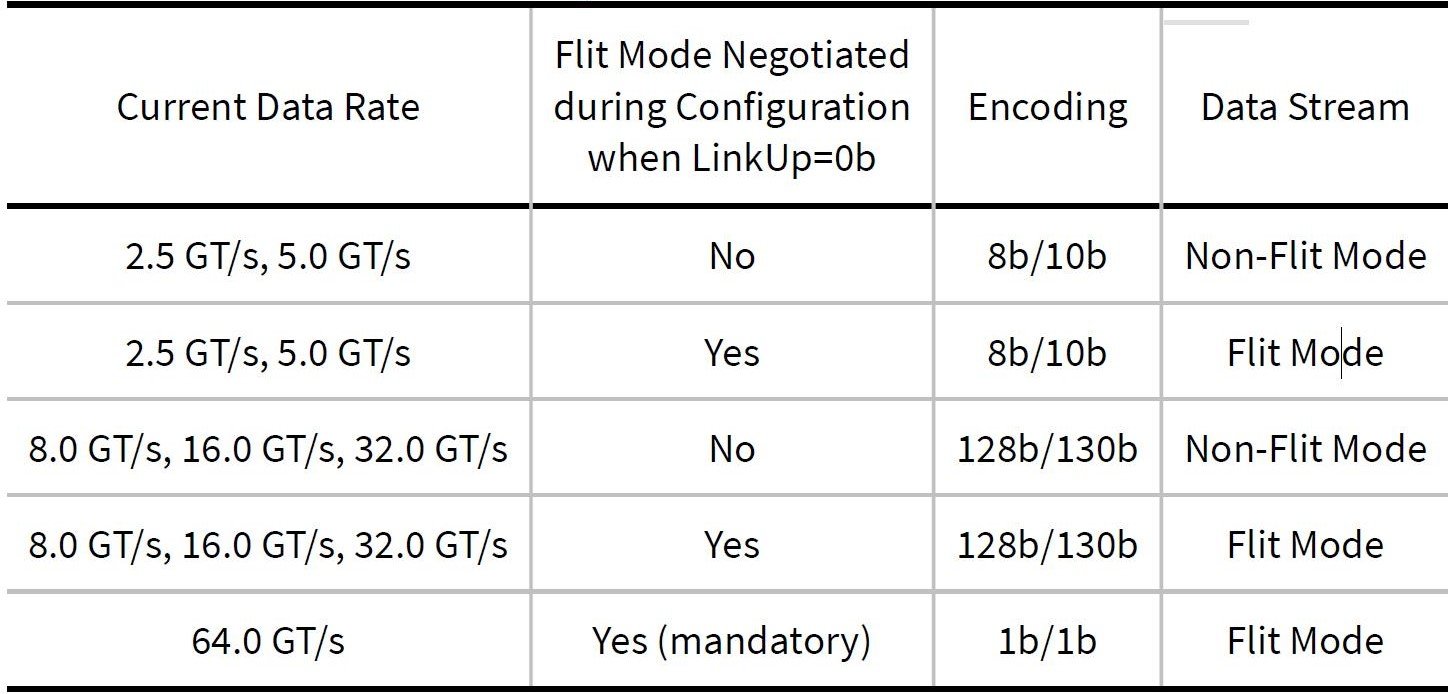

PCIe 6.0도 흐름 제어 장치 (Flow Control Unit) 모드가 있으며 고정 패킷 크기(Fixed Sized Code Words)로, 이전 버전의 non-Flit 모드 및 인코딩 방식과 비교하여 PCIe 6.0은 필수 사용이 필요합니다. 전송을 위한 Flit 모드와 인코딩 방식도 기존의 8b/10b 및 128b/130b 코드와 달리 전송되는 모든 정보 비트가 유효한 코드임을 의미하는 1b/1b로 변경되었습니다.

또한 PCIe 6.0은 에너지 효율 측면에서도 PCIe 5.0보다 우수합니다. PCIe 6.0은 데이터 전송을 유지하면서 대역폭을 유연하게 조정해 활용도를 높이고 전력 소모를 줄일 수 있는 저전력 모드인 L0p가 새롭게 탑재돼 서버급 제품에는 큰 장점이다.

그림 5: 유효한 인코딩 및 데이터 흐름 조합(출처: PCIe Base Spec Revision 6.0.1)

PCIe 6.0의 이퀄라이제이션 측면에서 송신단은 FFE를 사용하고 수신단은 CTLE와 DFE를 조합하여 사용하지만 위에서 언급한 PAM41 인코딩 형식으로 인해 각 아이(Eye)의 진폭이 줄어들어 PAM4가 기호간 간섭에 더 취약하다는 사실을 보완하기 위해 PCIe 6.0의 DFE가 PCIe 5.0의 3-Tap에서 16-Tap으로 변경된 것을 볼 수 있습니다.

GRL PCIe 6.0 자동 보정 및 테스트 솔루션

PCIe 6.0 표준 기본 사양(Base Specification)은 완전히 초안이 작성되었지만 CEM(Card Electromechanical) 사양 및 PHY 테스트 사양은 아직 버전 5.0 상태입니다.

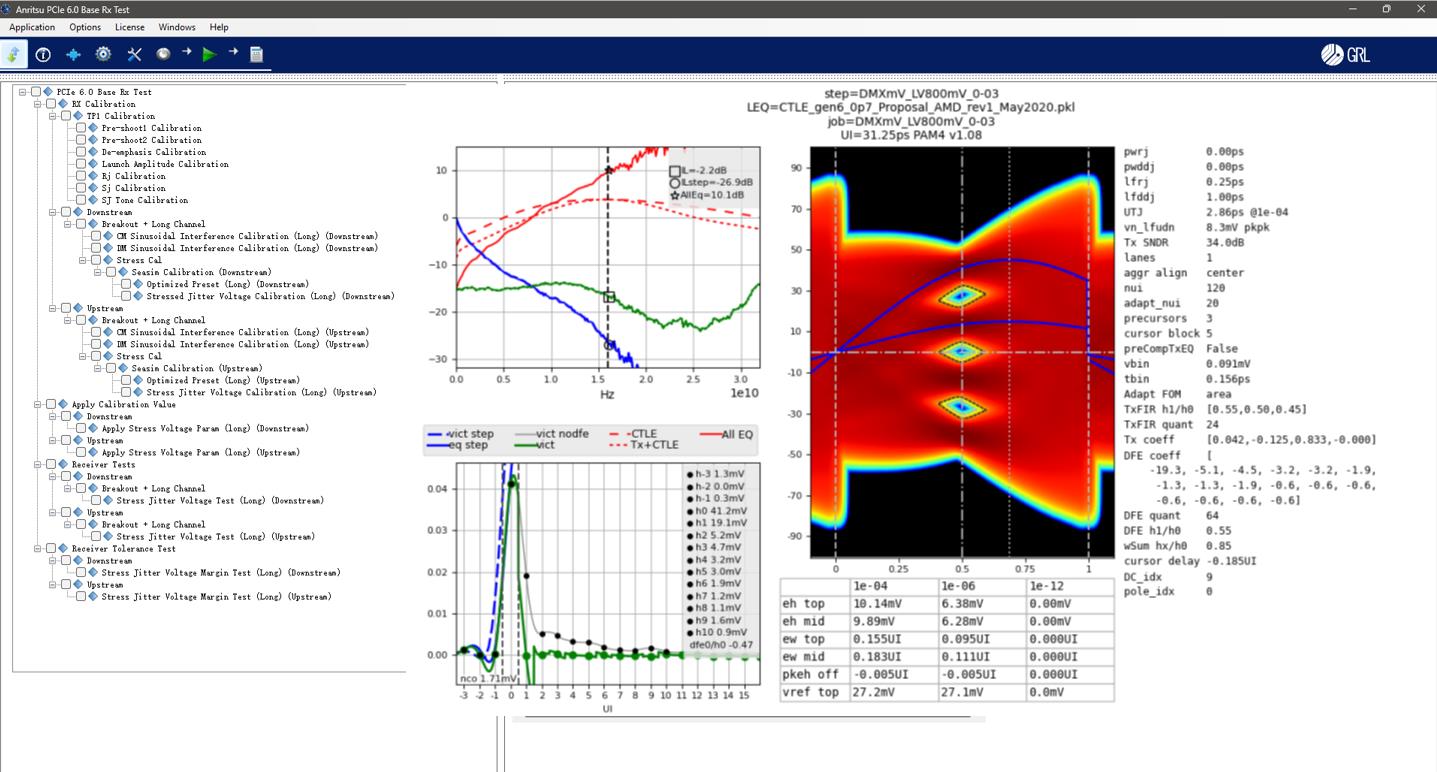

PCI-SIG 협회의 선례를 따라 GRL은 PCIe 5.0 및 이전 세대를 포함한 테스트 서비스 및 솔루션을 제공할 수 있을 뿐만 아니라 PCIe 6.0용 GRL-PCIE6-BASE-RXA 자동 보정 및 테스트 솔루션을 출시할 수 있습니다.

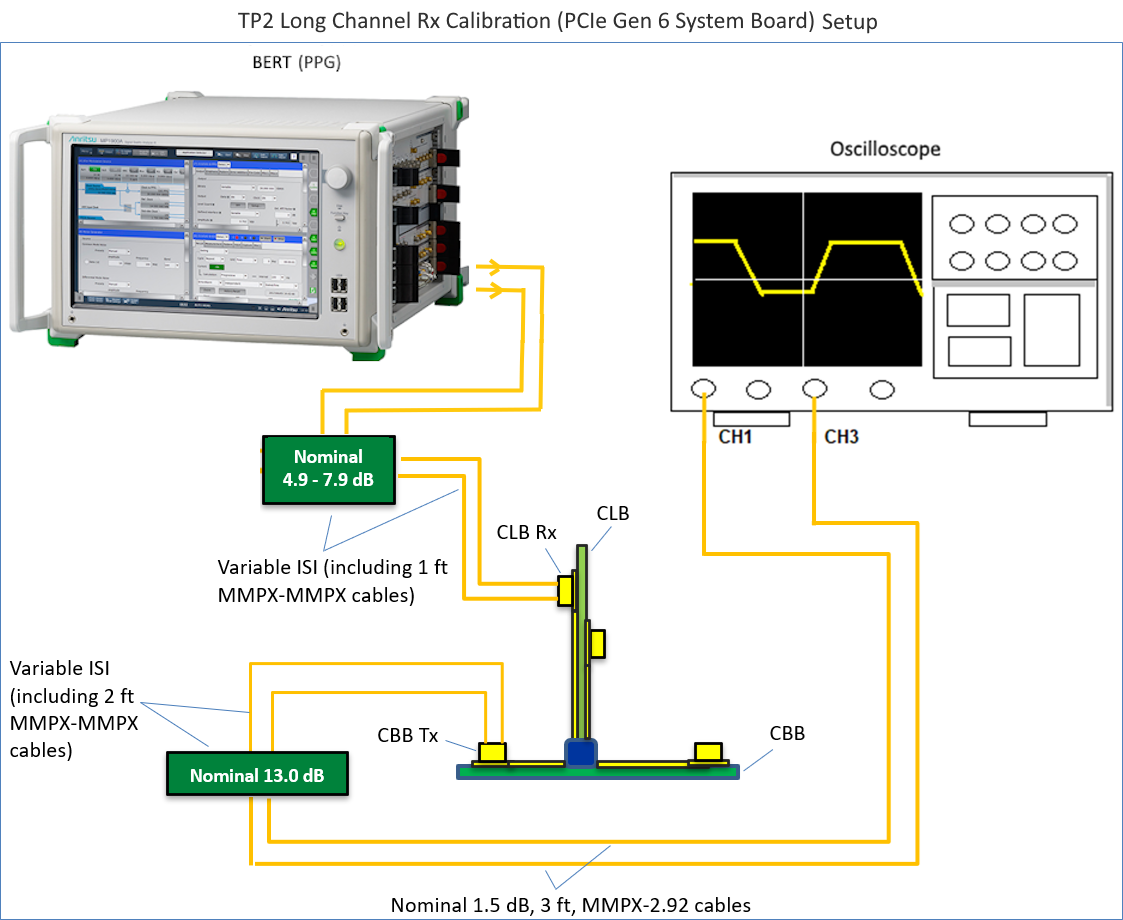

그림 6: GRL-PCIE6-BASE-RXA 자동 보정 및 테스트 솔루션

결론

위 내용은 PCIe 6.0의 PAM4 인코딩 방식 및 관련 기능(FBER, FEC, Flow Control Unit)을 소개한 것입니다. PCIe 6.0은 사용자에게 궁극적인 경험을 가져다 줄 것이며, 또한 생산 및 연구 개발 부서에 다양한 도전을 가져올 것이라고 믿습니다. GRL은 협회의 새로운 표준, PCIe의 급속한 발전에 발맞춰 고객에게 고급 종합 테스트 서비스 및 테스트 솔루션을 지속적으로 제공하고 더 나은 원스톱 서비스 경험을 제공합니다.

Reference

- PCI-SIG, PCI Express® Base Specification Revision 6.0.1

- Advancing Artificial Intelligence and Machine Learning Applications, Vamshi Kandalla, Granite River Labs

Author: GRL Dongguan 테스트 엔지니어 Winson Mok

GRL 테스트 엔지니어 Winson Mok 신호 무결성 및 스토리지 테스트 분야에서 수년간 근무한 경험이 있으며 Thunderbolt, PCI Express, USB 및 이더넷과 같은 다양한 테스트 사양에 익숙하며 현재 GRL Dongguan Storage 테스트를 담당하고 있습니다.

이 문서의 사양 및 설명은 사전 통지 없이 변경될 수 있습니다.

2023/02/09 AN-230209-TW

.png)

/PCIe%20Overview_featured%20image.jpeg)