Granite River Labs, GRL

吳明倫 Klay Wu

SATA自2003年發布後以多項優勢取代PATA。第一代SATA 1.0 (Gen1) 速率為1.5 Gbit/s;而隔年推出的SATA 2.0 (Gen2),速率升級至3.0 Gbit/s。再來直到2009年發布了完整的SATA 3.0 (Gen3),速率達到6.0 Gbit/s。

SATA測試波形的分類

應用於SATA測試的波形分為以下兩類,並且兩種不同的波形會應用於不同的測試驗證。

- Non-compliant patterns,用於進行下列測試:

- Jitter measurements

- Physical connection media tests

- Electrical parameter testing

- Compliant patterns,用於進行下列測試:

- Frame Error Rate testing

- In-system tests

接下來,將詳細介紹兩種類型的波形,分別包含Non-compliant patterns的四種波形以及Compliant patterns的兩種波型。

Non-compliant patterns介紹

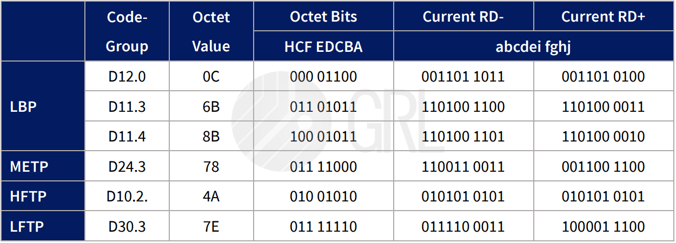

Non-compliant patterns主要有四種,包含Lone Bit Patterns (LBP)、High Frequency Test Pattern (HFTP)、Mid Frequency Test Pattern (MFTP)、Low Frequency Test Pattern (LFTP)。下方將為大家一一介紹各波形的組成。

- Lone Bit Patterns (LBP)

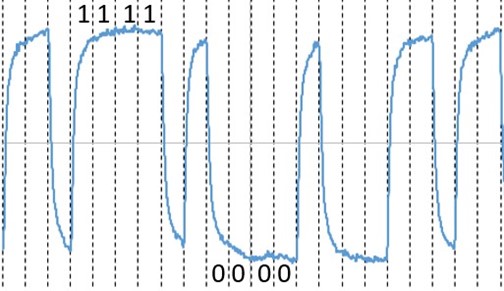

LBP是由8b/10b編碼模式所組合而成,其中包含D12.0、D11.3、D11.4三種波形以特定方式組合。而這種訊號裡面一定會出現連續4個1或4個0,如下圖記號所表示。此訊號用於抖動的測量。

圖1: Lone Bit Patterns (LBP)波形

- High Frequency Test Pattern (HFTP)

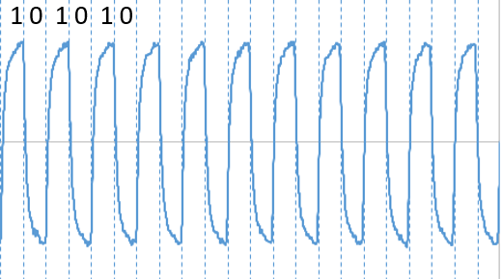

HFTP由連續的D10.2組成,主要用於Unit interval (UI)與Spread Spectrum Clocking (SSC)的相關測試。

圖2: High Frequency Test Pattern (HFTP)波形

- Mid Frequency Test Pattern (MFTP)

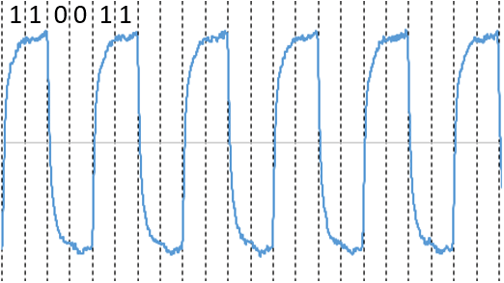

MFTP由連續的D24.3組成,UI為HFTP的兩倍,主要用於Emphasis的測試。

圖3: Mid Frequency Test Pattern (MFTP)波形

- Low Frequency Test Pattern (LFTP)

LFTP由連續D30.3組成,隨著規範更新,測試進行時不會使用LFTP。因此這個波形僅為測試前的校正程序所使用。

表1: Non-compliant patterns波型總整理

圖4:HFTP(綠)、MFTP(黑)、LBP(藍)三種波型比較

Compliant patterns介紹

Compliant patterns主要有兩種:Compliant Framed Composite patterns (FCOMP)與Compliant Lone Bit Patterns (LBP);因Compliant Lone Bit Patterns (LBP)即為前面所介紹過的Non-compliant LBP,是在加入些許限制與修飾後,而具備Compliant patterns的特性。下方將著重在FCOMP的介紹。

– Compliant Framed Composite patterns (FCOMP)

FCOMP有以下三種變化,主要用於量測抖動。

- Low Frequency Spectral Content Pattern (LFSCP),特徵為三個連續的1搭配一個0或是三連續的0搭配一個1。

- Low transition Density Pattern (LTDP),主要由三個或四個連續的1或0所組成。

- High transition Density Pattern (HTDP),由單個1與0所形成的全速率模式,加上兩個1與0的半速率模式所形成。

電性基礎特性與訊號測試介紹

以下為三個主要會應用到SATA測試波形的測試項目:

- 電性基礎特性 (Phy general)

- 電性傳輸訊號 (Phy transmit signal)

- 電性接收訊號 (Phy receiver signal)

- 電性基礎特性 (Phy general)

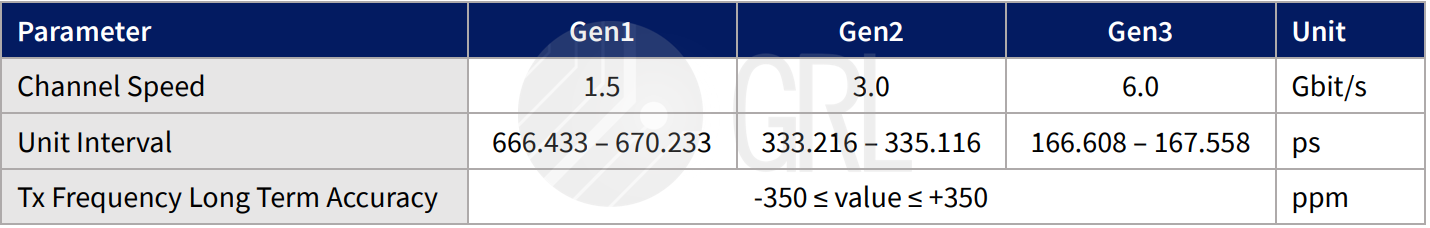

電性基礎特性簡寫為PHY,為Gen1/Gen2/Gen3共同必須測試的項目,其中包含UI與SSC的相關測試,需使用HFTP波形進行測試。

單位間隔(Unit Interval)是不包含抖動時的特定標稱值。而頻率長期穩定度(Frequency Long Term Accuracy)必須在正負350 ppm的規範之中。

表2: PHY測項與規範

- 電性傳輸訊號 (Phy transmit signal)

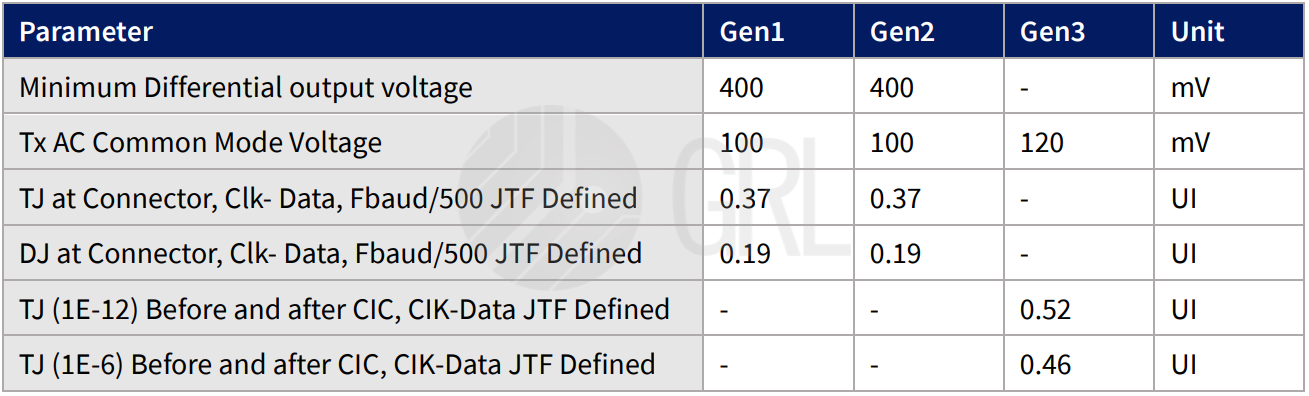

電性傳輸訊號測試簡寫為TSG,其中包含電壓大小、抖動以及Emphasis,需使用HFTP、MFTP、LBP等波形進行測試。

在發送端測得的最小差分電壓(Minimum Differential out put voltage)應符合相應的電氣規範,其中包括任何Pre-emphasis。此測試項目僅針對支援Gen1與Gen2的產品,需利用MFTP測試模式進行量測。

交流共模電壓(AC Common Mode Voltage)是指在發送端的連接器處,利用測試模式MFTP以及HFTP測得的最大正弦幅度。該數值是由於受到上升/下降不匹配和其他要求限制,所導致Tx+/Tx-的不匹配,用於衡量除去共模尖峰以外的共模噪聲。

抖動(Jitter)作為數據與相關事件之轉換的理想點,對於總抖動(TJ)與確定性抖動(DJ)測量規範在Gen1/Gen2以及Gen3有不同的定義,測試時須利用HFTP與LBP測試模式進行量測。

表3: TSG測項與規範

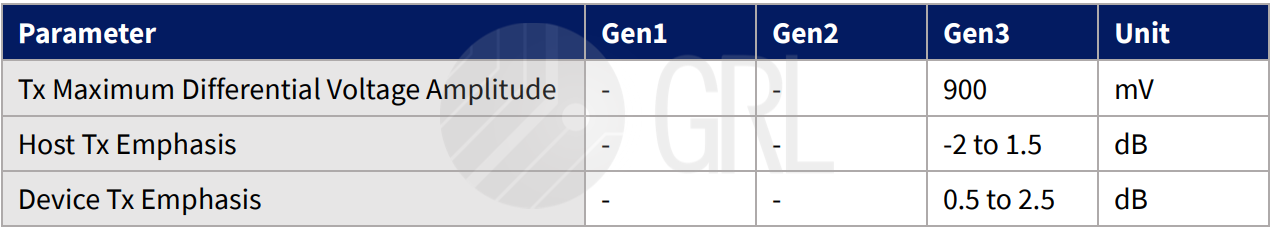

而最大差分電壓幅度(Maximum Differential Voltage Amplitude)與Emphasis的量測,僅對於支援Gen3之產品,且須利用MFTP測試模式進行量測。

表4: TSG測項與規範

- 電性接收訊號 (Phy receiver signal)

電性接收訊號測試簡稱RSG,主要量測內容為接收抖動容許限制以及應力測試,測試時使用FCOMP波形,校正時則需要用到FCMOP、LBP與LFTP等波形。

抖動容限測試將針對特定頻率點10、33、62、5 (MHz)進行。應力測試則針對62 MHz的頻率點進行。

結論

SATA測試波形主要有HFTP、MFTP、LBP與FCOMP,其中HFTP、MFTP與LBP運用於PHY、TSG測試,FCOMP與修飾後LBP運用於RSG測試。測試時應將測試模組建立於待測物IC之中,並透過適當的設定,可利用指令讓待測物生成測試波形,或是藉由波形產生器取代指令。

參考文獻

- UTD_1_6_Rev1_1 Released

- SerialATA_Revision_3_5a_Gold

- Altera Corporation Specifications and Additional Information

作者

GRL 台灣測試工程師 吳明倫 Klay Wu

具USB、SATA、PCIe介面相關測試經驗,協助客戶在USB-IF方面取得認證。

本文件中規格特性及其說明若有修改恕不另行通知。

發佈日期 2022/06/13 AN-220613-TW

/SAS%20and%20SATA%20Overview_featured%20image.jpeg)