Granite River Labs, GRL

Wing Tseng 曾威華

本篇文章我們將介紹 USB 3.2 的物理層(Physical Layer)測試。在物理層測試當中,分為傳送測試(Transmitter)以及接收測試(Receiver)兩大部分;傳送測試可比喻成驗證 USB 產品的說話能力,接收測試則比喻為 USB 產品的聽力,通過測試認證的 USB 產品就應當有著穩定的訊號傳送及接收能力。USB 3.2 在開始傳輸資訊之前,會先使用 LFPS 訊號先行溝通,這種低頻週期訊號可節省產品功耗,所以在物理層的訊號測試也會對 LFPS 訊號進行測試。

USB 3.2 傳送測試(Tx Test)

-LFPS 發送測試

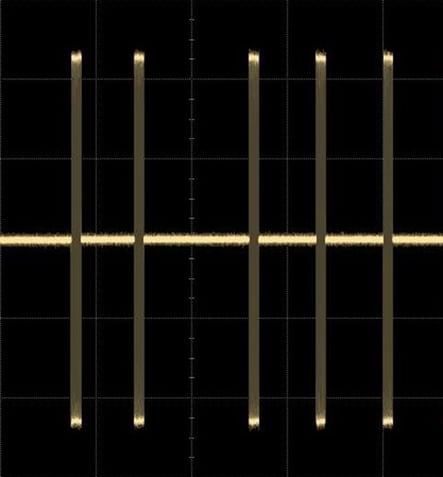

在 USB 3.2 物理層 CTS(Compliance Test Specification)中,規定使用待測物(DUT)前五個發送的 LFPS Bursts 來做測試,下圖為 SCD1 在示波器上的波型:

圖 1

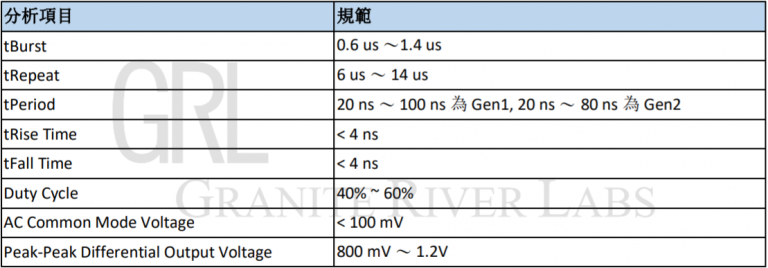

接著將利用擷取到的 LFPS 波型來分析測試,分析項目和規範如下表:

表 1

由規範可發現測試對 LFPS 的 Burst 相關時間長度及上升、下降時間和占空比(Duty Cycle)有所要求,另外在 AC Common Mode Voltage 和 Peak-Peak Differential Output Voltage 對於差分訊號相加或相減之後的規範,代表兩個差分訊號的相位差及電壓大小不可相差太多。

USB 3.2 Gen1 及 Gen2 傳送測試

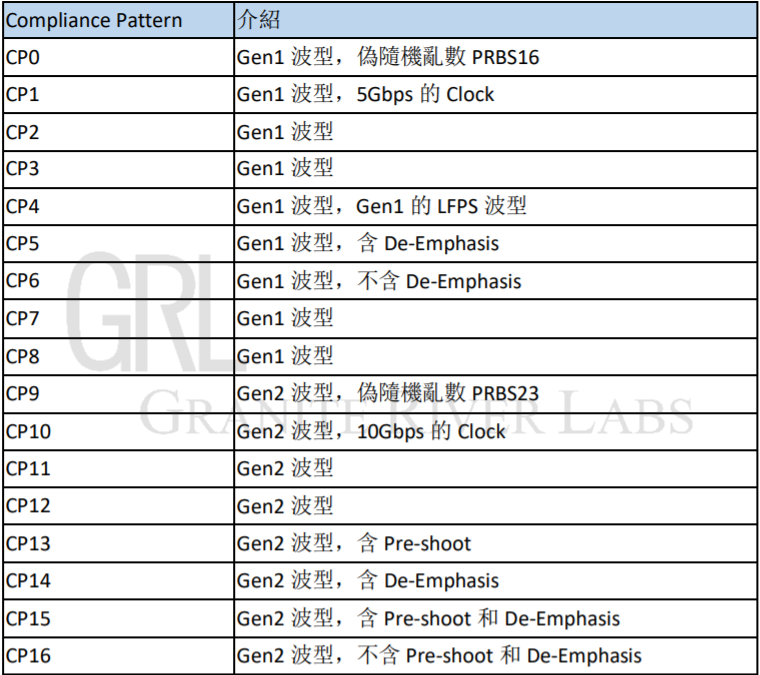

在此測試中需要將待測物進入 Compliance Mode,此模式共有 17 種 Pattern,整理介紹如表二:

表 2

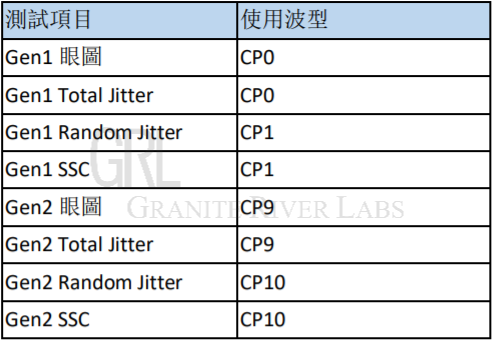

接著我也將測試項目還有其對應的測試波型整理如表三:

表 3

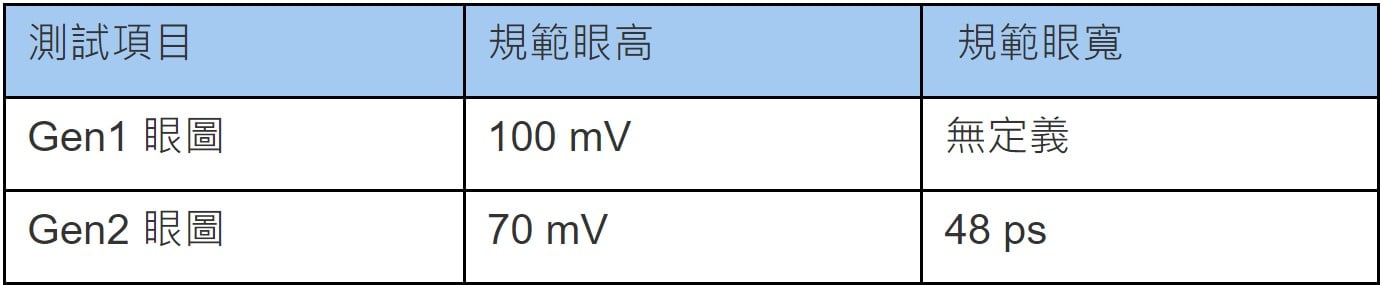

眼圖測試代表訊號的基本品質,每一個 Unit Interval 都不壓到 Eye mask 表示發送的訊號能準確的區分邏輯 0 和邏輯 1,電壓大小及抖動量也都有在一定的規範內。眼圖的規範範圍如表四:

表 4

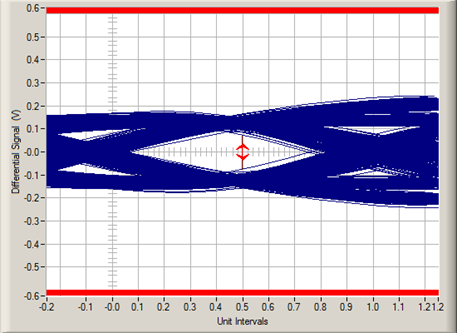

附上 USB 3.2 Gen2 的 Long Channel 眼圖如下圖供大家參考:

圖 2

Gen2 的 Tx EQ 測試代表了 USB 晶片發送訊號的 EQ 調整量要在規範範圍表五之內:

表 5

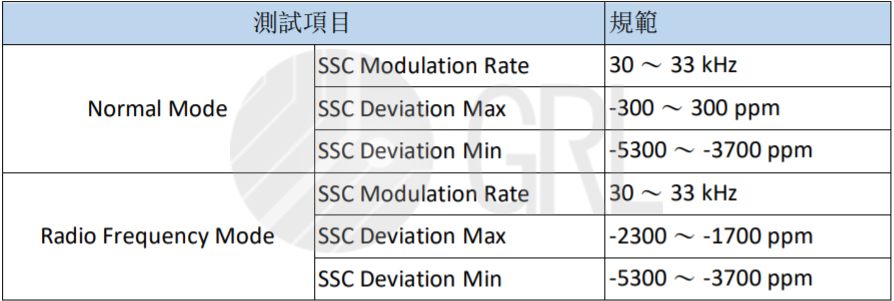

最後是 SSC 測試,在目前越來越高速傳輸的介面會產生電磁干擾(EMI),USB-IF 協會使用了展頻時脈 SSC(Spread Spectrum Clock)的方式來降低傳輸訊號在同一個頻率上的頻譜振幅,也進而減少了電磁干擾。

SSC 的原理類似我們的頻率調變(Frequency Modulation),對傳輸訊號做一個三角波週期的頻率調變。圖三為 Normal Mode SSC 三角波週期調變範圍。

.png?width=547583&name=%E5%9C%96%E7%89%873-3%20(1).png)

圖 3

表六為 SSC 測試項目及其規範:

表 6

USB 3.2 接收測試(Rx Test)

-LFPS 接收測試

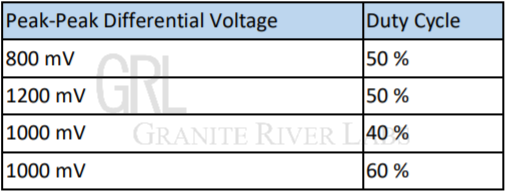

此測試只針對 USB 3.2 Gen1 的訊號做測試,測試目的是希望待測物能夠正確的接收到 Link Partner 的 LFPS。測試原理儀器端會發送四種較差的 LFPS 給待測物,若待測物接收到這四種 LFPS 還能夠順利溝通並回傳 TSEQ 則代表通過此測試。下表為測試使用的四種 LFPS:

表 7

USB 3.2 Gen1 及 Gen2 接收測試

在接收測試中,要使待測物進入 Loopback Mode。在此模式時,USB 產品會回傳收到的訊號,測試目的為 USB 產品在接收訊號上能夠準確判斷 Link Partner 在傳送的訊號,所以測試上儀器會先與待測物溝通進入 Loopback Mode,接著開始發送測試訊號,當中測試訊號會加上一定的抖動頻率及其對應的抖動量給待測物,待測物接收到測試訊號後回傳給誤碼儀(Error Detector),只要小於等於 1 個 Bit Error,表示待測物通過 Rx 測試。

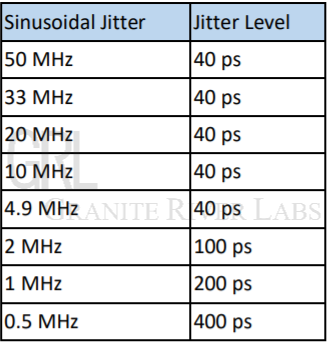

USB 3.2 Gen1 共有 8 個 Sj 測試點,每點測試 3×1010 個 Bits,每點測試時間約為 6 秒鐘,測試點如表八:

表 8

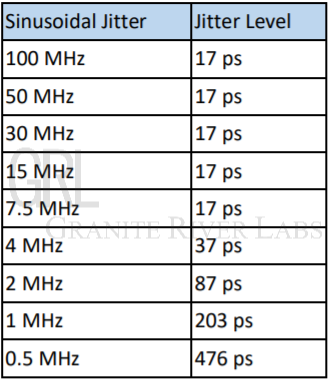

USB 3.2 Gen2 共有 9 個 Sj 測試點,每點測試約 1.2×1012個 Bits,每點測試時間約為 2 分鐘,測試點如表九:

表 9

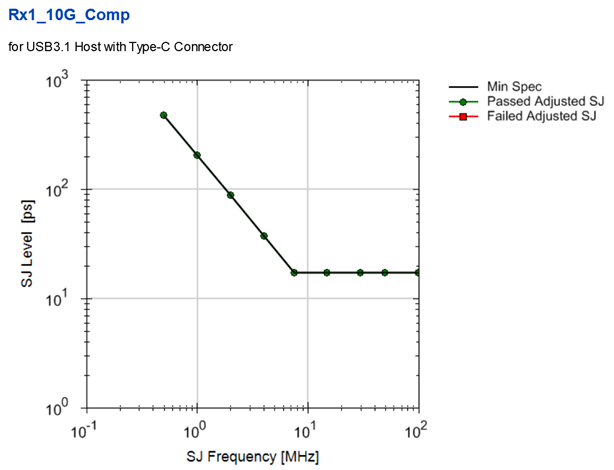

最後附上 USB 3.2 Gen2 接收測試的結果如下圖:

圖 4

參考文獻

- Universal Serial Bus 3.2 Specification, September 22, 2017

- Electrical Compliance Test Specification Enhanced SuperSpeed Universal Serial Bus, February 14, 2017

作者

GRL 台灣技術工程師 曾威華 Wing Tseng

擅長 USB、PCIe、SATA 介面測試。GRL 技術文章作者及講師。希望幫助大家順利測試拿到介面 Logo,彼此互相交流共同成長飛翔。

本文件中規格特性及其說明若有修改恕不另行通知。

發佈日期 2019/05/20 AN-190503-TW