Granite River Labs, GRL

상해 Sea Chen

USB 3.2 Gen1의 루프백 모드는 USB 3.2 Gen1의 데이터 링크 계층(Link Layer)에 있는 모드로, 주로 USB 3.2 호스트(Host) 또는 디바이스(Device)의 비트 오류율 테스트를 수신하는 데 사용됩니다.

실제 테스트에서 어떻게 DUT를 루프백 모드로 원활하게 진입시키는가가 USB 3.2 Gen1 수신기 테스트를 원활하게 통과할 수 있는지 여부가 관건이므로 이 글에서는 USB 3.2 Gen1의 동작 모드를 소개하고 USB의 동작 모드에 대해 설명하고자 합니다. 3.2 Gen1 Gen1 테스트에서 테스트 장비는 DUT를 루프백 모드로 전환합니다

USB 3.2용 데이터 링크 계층 교육 및 링크 교육 상태 기계(LTSM)

1. 작업 상태

LTSSM의 정식 명칭은 Link Training and Status State Machine으로, 주로 링크 상태와 링크의 전원 관리를 제어하는 데 사용됩니다. U0-U3의 4가지 작동 상태가 있습니다.

- U0 상태는 초고속링크가 허용된 상태, 즉 정상 작동 상태, 데이터 패킷이 전송중이거나 데이터 링크가 유휴 상태임을 나타냅니다.

- U1은 저전력 데이터 링크 상태를 나타내며 이때 데이터 패킷이 전송되지 않으며 초고속 데이터 링크는 전력 소비를 줄이기 위해 허용되지 않는 상태가 될 수 있습니다.

- U2는 또한 저전력 상태입니다(전력 절약이 추가되지만 이 상태를 종료하는 데 더 긴 대기 시간이 필요함).

- U3는 데이터 링크를 종료하고 장치는 일시 중단된 상태에 있습니다(전력을 추가로 절약할 수 있음).

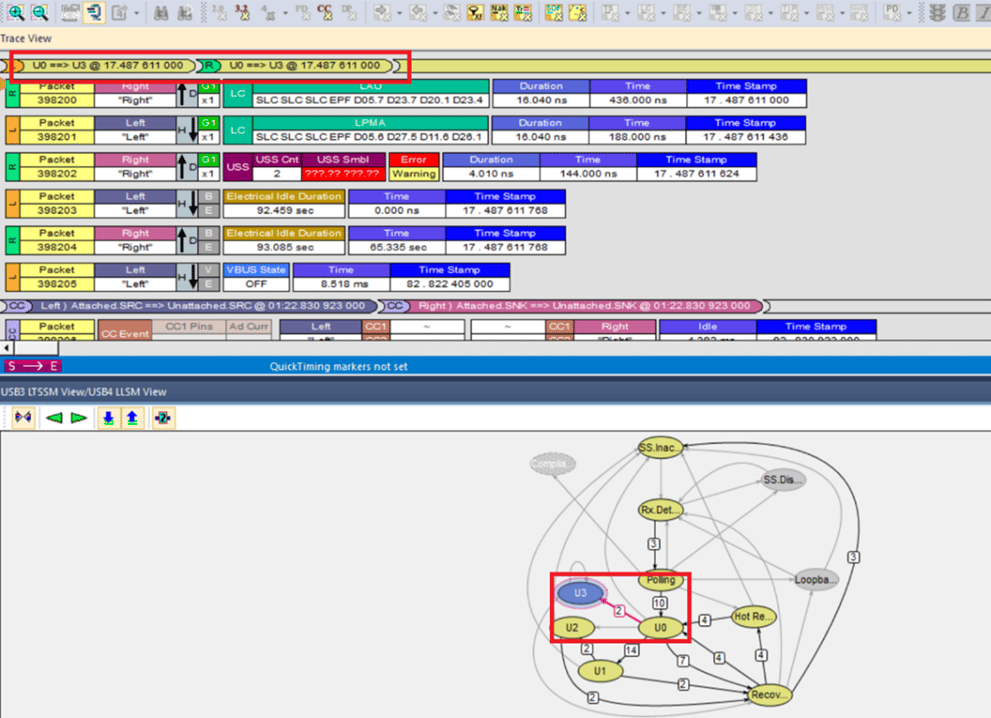

호스트(호스트)가 USB 3.2 장치를 정상적으로 인식한 다음 호스트를 작동하여 슬립 또는 재시작 프로세스로 들어가면 U0-U3의 다음과 같은 다른 상태를 캡처할 수 있습니다. (아래 사진은LeCroy USB 3.2 프로토콜 분석 기준)

그림 1: LeCroy USB 3.2 프로토콜 분석 - Status U0-U3

그림 1: LeCroy USB 3.2 프로토콜 분석 - Status U0-U3

2. 연결 상태

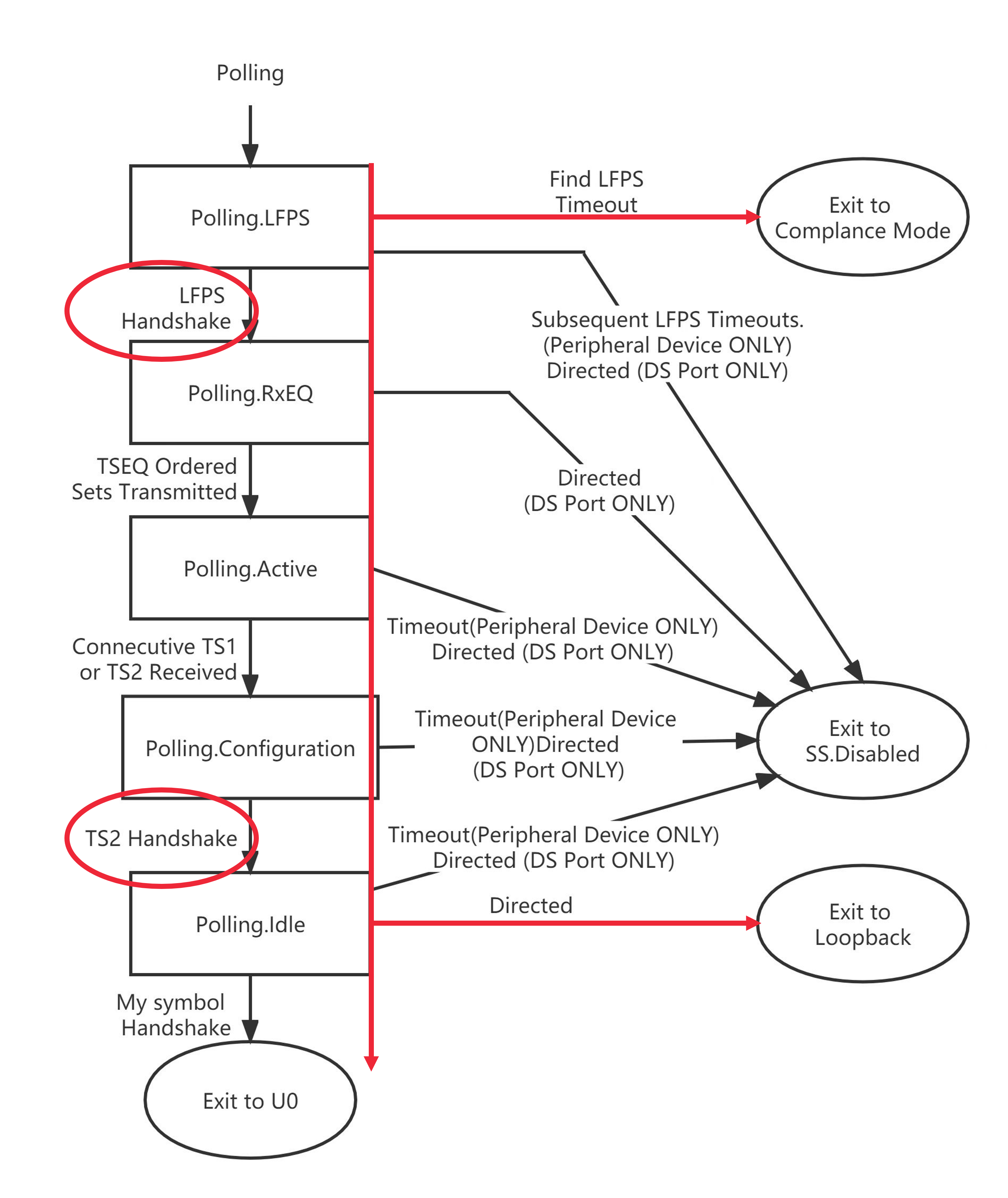

USB 3.2 개정판 1.0 사양에서 LTSSM 링크 훈련 상태 머신 흐름도(그림 2)에 RX.Detect, Polling, Recovery 및 Host Reset의 네 가지 연결 상태가 있음을 알 수 있습니다.

그림 2: LTSSM 링크 훈련 상태 머신 순서도

- Rx.Detect: 연결의 전원이 켜졌을 때 호스트와 장치가 서로의 존재를 인식할 수 있음을 나타냅니다. 인식되면 두 당사자는 초기화 교육 프로그램에 들어가기 시작합니다.

- Polling: 호스트와 장치가 발신자와 수신자를 초기화하고 동기화하고 데이터 패킷을 보낼 준비가 되어 있음을 나타냅니다.

- Recovery(데이터 복구): 주로 현재 연결이 현재 시스템을 저전력 상태에서 전환해야 하거나 현재 U0 상태에서 작동하지 않는 것을 발견하고 연결을 복원하도록 재교육 및 구성해야 할 때입니다.

- Host Reset: 링크를 통해 다운스트림 포트가 업스트림 포트를 재설정할 수 있음을 나타냅니다.

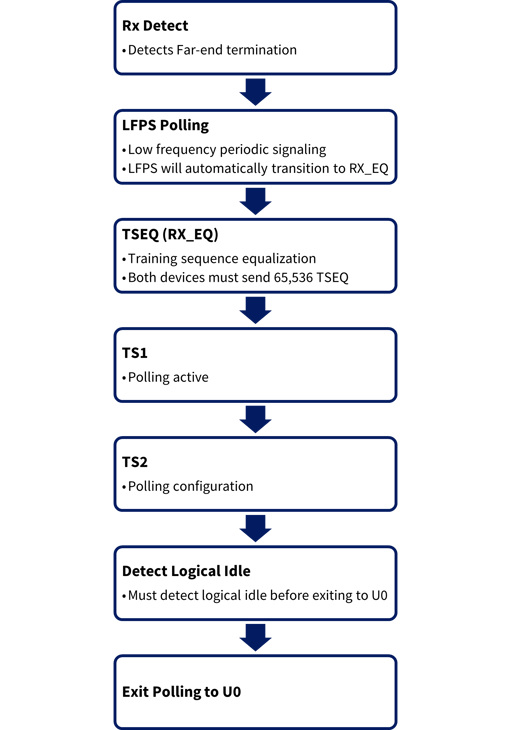

그림 2에는 비트 오류율 테스트와 송신기 표준 테스트를 위해 도입된 루프백(Loopback)과 적합성 모드(Compliance Mode)의 두 가지 다른 연결 상태가 있으며, 다른 두 상태는 연결 오류로 인해 각각 발생하는 SS.Inactive 및 SS.Disabled입니다. 작동 불가 상태에서 링크는 비초속 모드에서 작동 중이며 USB 2.0 모드일 수 있습니다. 일반적으로 사용) 펜 드라이브는 노트북 컴퓨터를 삽입하고 데이터를 정상적으로 읽는 과정까지) Rx.Detect, Polling, U0의 3단계를 거쳐야 합니다. Polling 과정은 연결된 단말 장비를 초기화 하는 과정으로 Rx.Detect부터 U0까지의 단계는 다음과 같습니다.

그림 3: U0 서브루틴 단계에 대한 Rx.Detect

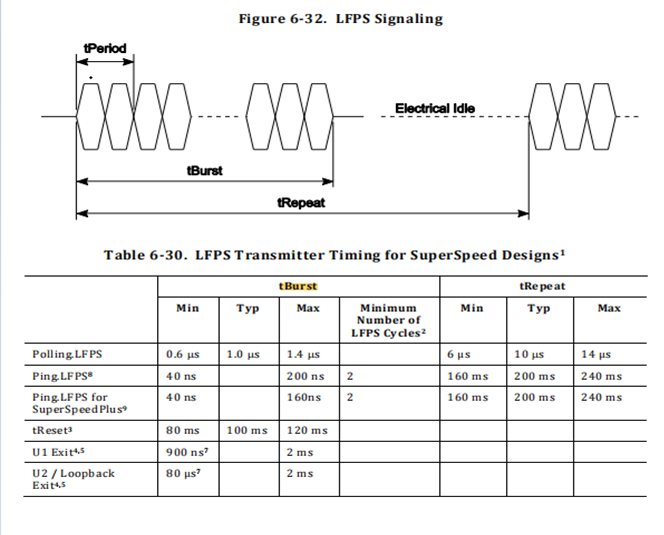

Rx.Detect 단계에서 연결된 호스트 또는 장치는 상대방에 단말이 있는지 확인하기 시작하고 단말이 있으면 연결된 단말은 특정 사양의 Polling.LFPS 코드(저주파 주기적 버스트) 전송을 시작합니다. 신호, 주기는 20ns ~ 100ms), LFPS 신호는 매우 중요한 신호입니다.호스트 또는 장치는 특성이 다른 LFPS 신호를 통해 다른 설치 상태 사이를 전환할 수 있습니다.특성이 다른 LFPS 신호는 주로 타이밍의 차이를 나타냅니다. , 예를 들어 tBurst 및 tRepeat 매개변수. 다양한 요구 사항에 대한 LFPS 신호 매개변수는 그림 4에 나와 있습니다(출처: USB3 사양).

그림 4: LFPS 신호 정의

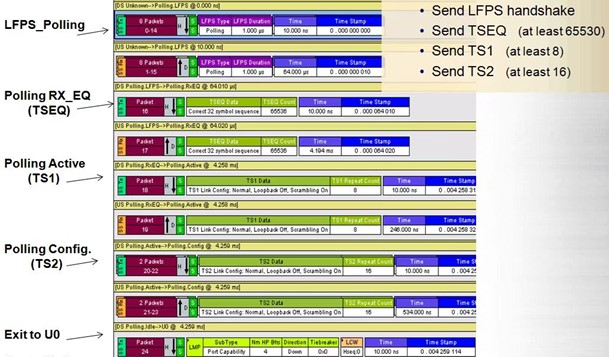

Polling.LFPS의 특정 시간 후, 먼저 Polling.RxEQ의 포트에 입력하고 설정된 TSEQ 코드 전송을 시작하여 수신 측에서 이퀄라이저를 설정한 다음 TS1/TS2(트레이닝 시퀀스, 트레이닝 코드)를 사용하여 다른 관련 설정 , 마지막으로 Idle 코드를 전송하여 전체 연결 초기화를 완료하고 U0 작업 상태로 전환하여 사용합니다. 그림 5는 르크로이 USB 3.2 분석기에 의한 연결 초기화 과정을 분석한 결과이며, 이 그림에서 연결 초기화 과정의 세부 훈련 코드 시퀀스와 타이밍 관계를 알 수 있다.

그림 5: 연결 초기화 프로세스

수신기 비트 오류율 테스트

연결된 호스트 또는 장치에서 비트 오류율 테스트를 수행해야 하는 경우 DUT는 그림 6과 같은 루프백 모드로 들어가야 합니다.

그림6: 루프백 훈련

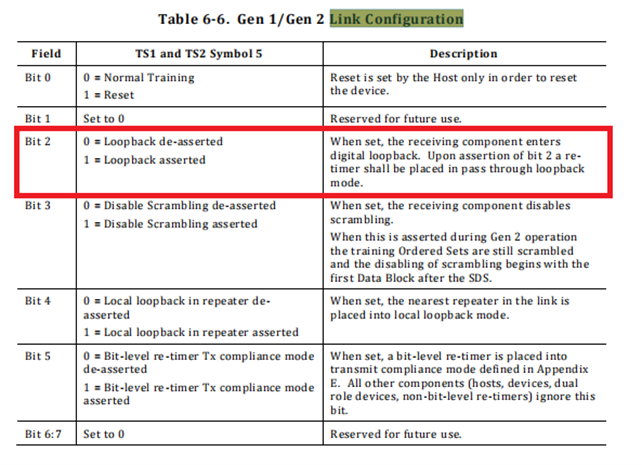

그리고 USB 3.2 사양에 따르면 루프백 모드로 들어가야 하는 경우 루프백 마스터와 루프백 슬레이브가 있어야 하며 루프백 마스터는 루프백을 요청하는 포트이고 루프백 슬레이브 포트는 수신된 심볼을 전송합니다. 루프백 마스터에서. 루프백 마스터는 U0 진입의 초기화 순서를 변경하지 않고 유지해야 하며, 이때 그림 7과 같이 훈련 코드 TS2의 다섯 번째 기호 Bit2만 루프백 모드로 설정하면 됩니다.

그림 7: Gen1/Gen2 링크 구성

루프백 모드로 들어가는 방법

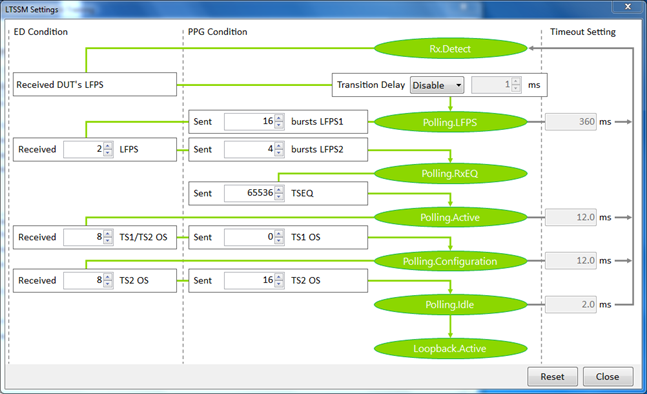

루프백 모드로 들어가는 가장 일반적인 방법은 신호 소스 또는 디지털 패턴 발생기를 루프백 마스터로 사용하여 특정 패턴 시퀀스를 DUT(루프백 슬레이브)로 보내 강제로 루프백 모드로 들어가는 것입니다. 8b/10b 데이터의 경우 루프백 슬레이브는 수신된 10비트 기호를 재전송하거나 필요한 경우 레인 극성 반전을 수행하고 SKP 순서 세트를 적절하게 삽입 또는 제거해야 합니다. 그림 8은 Anritsu의 MX183000A의 USB 링크 교육을 사용하여 루프백 교육 중에 전송된 디지털 패턴 생성기 및 매개변수 설정을 보여줍니다.

그림8: Anristu MX183000A를 통한 LTSSM 설정

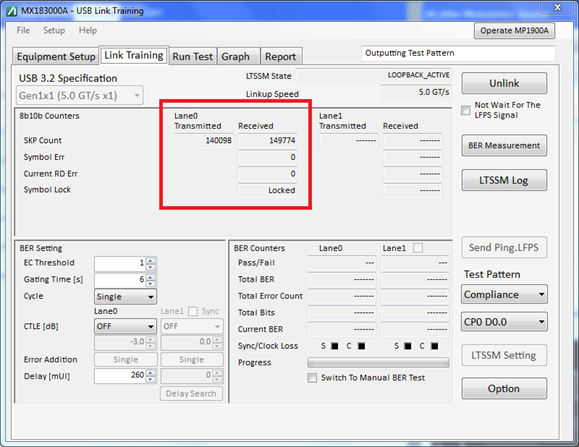

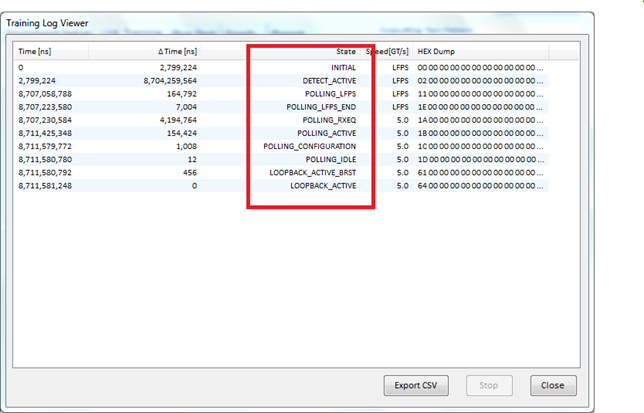

루프백 모드에 성공적으로 들어간 후 USB Link Training 인터페이스는 그림 9와 같이 표시되어야 하며 링크 상태는 Loopback.Active이며 LTSSM 상태 머신에 의해 인쇄된 특정 훈련 로그는 그림 10에 나와 있습니다.

그림 9: Anristu MX183000A를 통한 USB 링크 교육

그림 10: LTSSM 훈련 로그

결론

이 기사에서는 USB 3.2 Gen1 작동 모드, 연결 초기화 프로세스, LTSSM(Link Training State Machine) 워크플로, LFPS 신호 정의 및 루프백 구성을 소개하고 실제로 LeCroy USB 3.2 프로토콜 분석기를 사용하여 연결 상태 및 특정 Anritsu LTSSM 구성 및 MX18300A USB 링크 교육의 상태에 대한 세부 정보가 루프백 모드에 성공적으로 진입했습니다. Loopback 모드는 USB 인증 테스트의 매우 중요한 부분이므로 저자는 독자들이 이 기사를 통해 Loopback의 동작과 방법에 대해 더 많이 배울 수 있기를 바랍니다. 그래야 실제 수신 측에서 제품을 보다 원활하게 테스트하고 관련 문제를 피할 수 있습니다.

참조

- USB-IF, Universal Serial Bus USB3.2 Specification, Revision 1.1, June 2022

Author

GRL 상하이 테스트 엔지니어 Sea Chen

7년의 테스트 경험을 가진 그는 현재 USB2 및 USB3 관련 기술의 제품 인증 테스트를 주로 담당하고 있으며 PCIE, SATA 및 기타 인터페이스 테스트에도 익숙합니다.

이 문서의 사양과 설명은 예고 없이 변경될 수 있습니다.

출시 날짜 2022/8/10 AN-220810-TW