何謂訊號完整性?

訊號完整性測量訊號從發送端到接收端無失真的傳輸程度。訊號傳輸過程中可能干擾訊號的環境因素包含:

- Crosstalk

- Ground bounce

- Jitter

- Mismatch

- Reflections

- Ringing

訊號完整性在印刷電路板 (PCB) 中為什麼重要

最小化環境對訊號完整性的影響是需要特別注意的。印刷電路板 (PCB) 是大部分電子設備中重要的組成之一,由絕緣玻璃纖維組件和導電銅金屬軌道製成的綠色板塊。由於高速訊號傳輸通常是PCB板上的瓶頸,訊號完整性分析可以幫助重新配置PCB,直到訊號能夠快速可靠地傳輸。

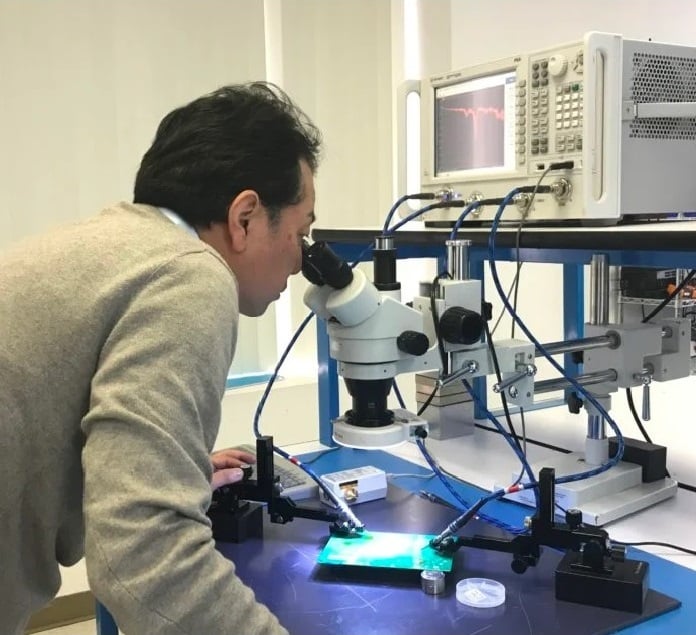

訊號完整性測試與分析

訊號完整性測試會在可控環境下進行,在發送端和接收端之間創建並模擬訊號傳輸;分析訊號完整性時,應確保以下因素不會影響測試結果:

- 橋接板

- 待測物焊接角度

- 量測方法

- 訊號線長

- 周圍干擾元素

- 測試點

通過檢查訊號品質、串擾和時序,能夠縮小訊號問題的原由。

訊號完整性中的VNA和TDR分析

VNA和TDR屬於數位訊號完整性測試。VNA透過掃描通過窄帶濾波器的正弦波並以同步方式掃描發送端和接收端來測量,可以檢查到S參數和系統損耗 (insertion and return loss) 等資訊。VNA數據需使用附加軟體轉換為時域,以便進一步了解待測物的構造。

TDR則是使用由寬頻寬等效採樣示波器和向待測物發送訊號的內部步進發生器組成的儀器進行測量的。TDR分析讓設計人員能夠測量出DUT屬性,例如錯誤發生位置、阻抗、時間延遲和系統構造。還可以使用時域傳輸 (TDT) 測量串擾、上升時間退化、回波損耗、集膚效應和介電損耗等更多特性。由於這種測量技術的瞬態特性,TDR結果是直觀的。頻率相關表現通常需要額外的軟體。

何謂電源完整性?

電源完整性是指流經驅動器和接收端的電流必須保持穩定,以可靠地發送和接收訊號。因此,電源完整性可以被認為是訊號完整性的其中一個部分,訊號完整性和電源完整性都是電路模擬與操作不可或缺的一部分。

電源完整性問題主要源於電壓紋波噪聲 (Ripple noise),它是在瞬變與通道電感發生反應時產生的。當AC轉換到DC時,電流瞬變又會產生。由於每個組件都連接到主電源,紋波噪聲可能通過串擾影響系統的任何部分。

來自未經過濾的交流電源的電磁干擾 (EMI) 是影響電源完整性的另一個常見因素。如果沒有適當的設計,EMI會影響無線訊號並導致串擾在電磁相容性 (EMC) 測試間出現。

電源完整性測試與分析

電源完整性分析涉及識別直流電源軌中斷和EMI問題,確保裝置設備可以穩定地傳輸足夠的電流以按預期工作。

電源完整性測試的參數可能很難定義,它們取決於訊號完整性元件。此外,高頻能量在通過傳輸平面分佈時在x和y方向上移動,也增加了分析的複雜性。雖然直流電平分析只需要計算軌跡、平面形狀和過孔的串聯電阻,但在更高頻率下還必須考慮電路板位置、安裝方法以及電容的位置、類型和大小等其他因素。

PCB設計指引

通孔 (Via)

Via是PCB中的電鍍通孔,用於追踪板的內層和外層。PCB通孔可以機械鑽孔和電鍍以創建電氣連接,由以下組件組成:

- Barrel: 填充滲透孔的導電管

- Pads: 電路板上的金屬裸露區域,用於焊接零件,也叫做焊盤或焊墊

- Antipads: 隔離孔與內層電器連接圍繞在孔周圍的隔離環

在多層板中,通孔為各層的電流和熱電流創建路徑,電流量將根據通孔尺寸和類型而變化。通孔類型包括:

- 通孔:最常見的通孔類型

- 盲孔:無法在PCB上找到,用於將電路板的表層連接到後續層

- 埋孔:PCB表面看不到,用於連接電路板的內層

疊層結構

PCB層堆疊在確定訊號完整性方面起著至關重要的作用。精細的層組織可防止共模電流阻抗的產生,因共模電流會產生RF能量,一旦RF能量進入配電網絡或自由空間,就會發出噪聲,從而產生干擾訊號的反射、振鈴或串擾。

另一方面,適當的PCB層疊可以有利於保持訊號完整性。例如高速走線可以是帶狀線,以最大化屏蔽和與相鄰接地板的內層磁通抵消。由於通過空氣耦合的風險較低,不太敏感的走線也可以在外部PCB層上形成微帶線 (microstriped)。

走線佈線

走線佈線在通孔和層堆疊完成之後進行,並且與PCB組件的定位方式密切相關。例如,逃離繞線 (escape routing) 必須仔細設計,以確保連接所有訊號,並確認旁路電容等相關組件盡可能靠近其引腳。

常見的佈線最佳方法包括:

- 訊號走線盡可能短和直接。

- 免敏感信號通過擁擠電路,例如模擬或電源部分。

- 為特定的線路拓撲預留足夠的空間。

- 盡量減少通孔以避免長度和電感可能會引入更多的訊號完整性問題。

- 盡可能將敏感的高速信號(例如clock line)與其他走線分開。並至少使用三倍的走線寬度。

- 將緊密佈線的差分對連接在一起,不要在障礙物(如通孔)周圍拆分差分對。

- 當對長度必須相等的網絡組進行佈線時,從最長的連接開始,向其餘連接添加調諧匝數,直到所有網絡達到相等長度。