Granite River Labs, GRL

Nicole Lan

MIPI(Mobile Industry Processor Interface)는 MIPI Alliance에서 시작되었으며 정식 명칭은 Mobile Industry Processor Interface로 모바일 산업 프로세서의 개방형 표준입니다. MIPI 얼라이언스는 2003년에 Texas Instruments(TI), STMicroelectronics(ST), 핀란드의 Nokia(Nokia) 및 영국 ARM에 의해 설립되었습니다. MIPI 얼라이언스는 개방형 회원제 조직으로 휴대전화 장비 제조업체, 시스템 공급업체, 소프트웨어 제조업체, 반도체 제조업체 및 기타 회사를 포함하여 휴대전화 업계의 모든 회사가 가입할 수 있습니다.

MIPI Alliance의 주요 목적은 모바일 장치의 칩셋과 주변 장치를 연결하기 위한 종합적인 사양을 제공하여 휴대폰의 내부 하드웨어 및 소프트웨어 인터페이스를 표준화하는 것입니다. 따라서 핸드셋 제조업체는 이러한 사양을 사용하여 성능을 최적화하고, 설계 프로세스를 간소화하고, 개발 비용을 줄이고 규모의 경제를 창출하며 출시 기간을 단축할 수 있습니다.

MIPI 인터페이스 및 멀티미디어 카테고리

MIPI 사양에는 6가지 유형의 인터페이스가 있습니다.

- Physical layer

- Multimedia

- Chip-to-chip/inter-processor communications

- Device control and data management

- System debugging

- Software integration

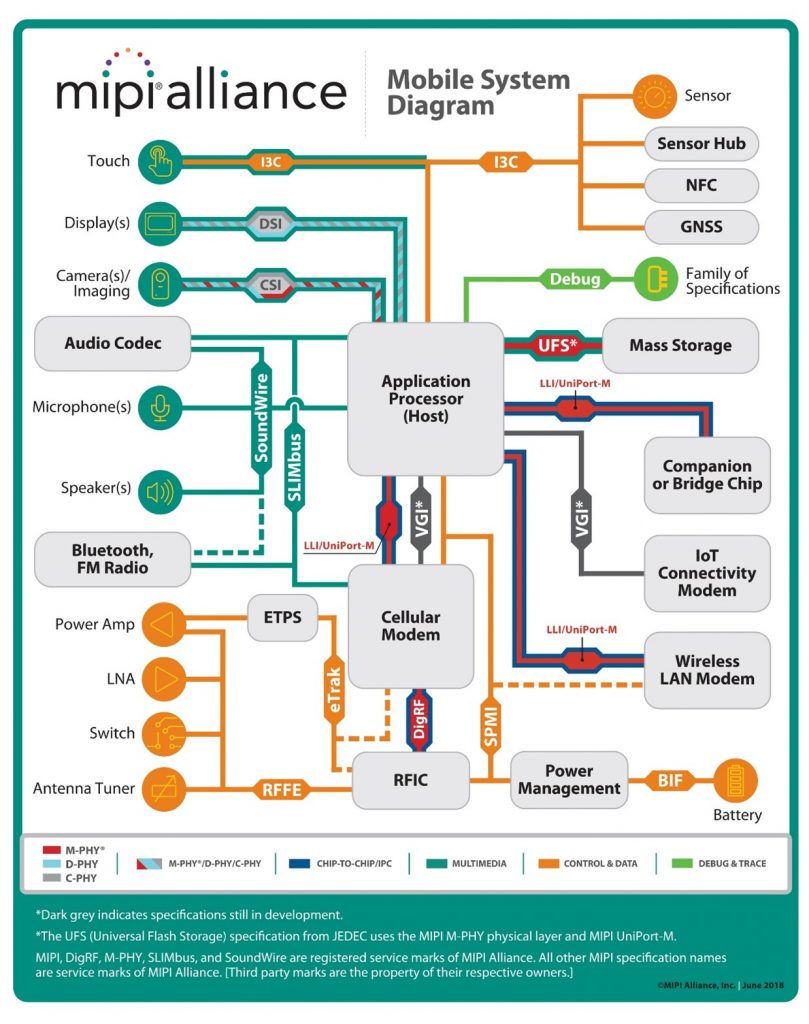

이러한 사양 각각은 모바일 기기에서 요구되는 엄격한 운영 조건, 즉 고대역폭 성능, 저전력 소비, 낮은 전자기 간섭(EMI)을 충족하기 위해 최적화되었습니다. 현재 MIPI 사양의 시스템 아키텍처는 다음과 같이 구성됩니다:

그림 1(https://www.mipi.org/about-us)

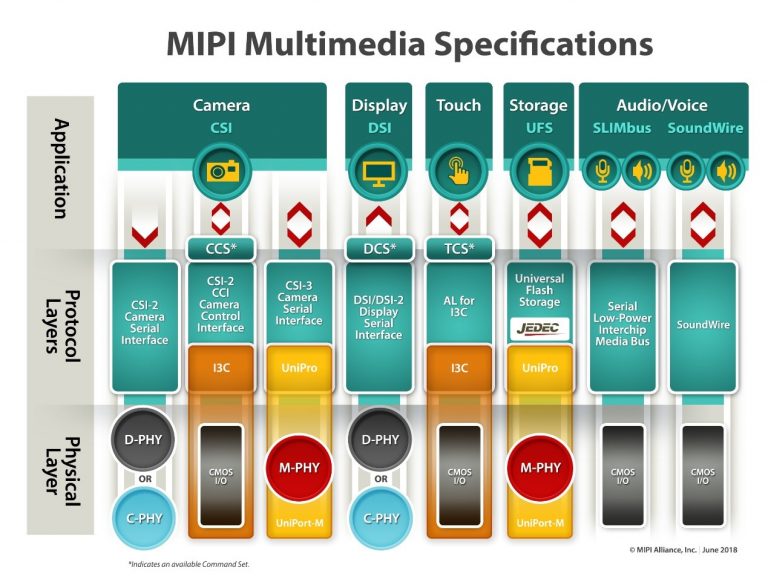

MIPI 사양의 멀티미디어(Multimedia) 범주는 주로 세 가지 수준으로 나뉩니다(그림 2).

- Application Layer

- Protocol Layer

- PHY Layer

이 중 이미지 전송과 관련된 CSI (카메라 시리얼 인터페이스)는 카메라 모듈과 프로세서 간의 고속 시리얼 인터페이스를 정의하며, DSI (디스플레이 시리얼 인터페이스)는 프로세서와 디스플레이 모듈 간의 고속 시리얼 인터페이스를 정의합니다. CSI-2와 DSI/DSI-2의 물리 계층에는 D-PHY와 C-PHY가 포함되어 있으며, 이 글에서는 CSI-2와 DSI/DSI-2의 물리 계층 중 D-PHY에 초점을 맞출 것입니다.

그림 2(https://www.mipi.org/about-us)

MIPI D-PHY 소개

MIPI D-PHY는 백만 화소 카메라와 고해상도 디스플레이를 애플리케이션 프로세서에 연결하여 유연하고 고속이며 저전력 및 저비용의 솔루션을 제공합니다. 동시에 링크 트랜시버의 마스터-슬레이브 관계로 인해 링크의 복잡성이 크게 감소되어, 주 데이터 전송 방향이 있는 디스플레이 및 카메라 케이스에 적합합니다.

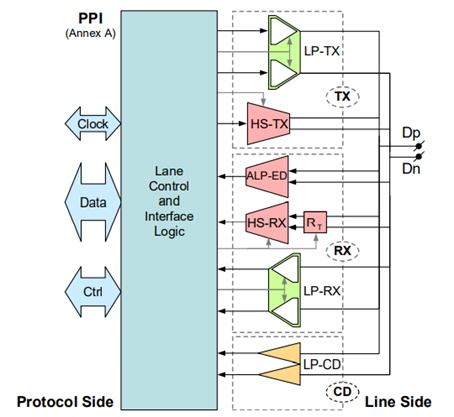

D-PHY의 구성은 클록 레인(Clock Lane)과 하나/다수의 데이터 레인(Data Lane)을 포함하며, 클록 레인은 모두 단방향 레인이며 데이터 레인은 단방향 또는 양방향 레인이 될 수 있습니다. 각 클럭 채널은 Cp, Cn을 포함하고 각 데이터 채널은 Dp, Dn을 포함합니다.

D-PHY의 각 링크에는 마스터 제어 터미널(Master)과 슬레이브 터미널(Slave)이 있으며 데이터 전송의 순방향은 마스터 제어 터미널에서 슬레이브 터미널로 진행됩니다. 마스터 제어단은 주 데이터 소스인 클록 채널에 고속 DDR 클록 신호를 제공하고, 슬레이브 단은 클록 채널에서 클록 신호를 수신하며 주 데이터 수신단입니다. 모든 경우에 클록 채널과 단방향 데이터 채널은 순방향 전송을 유지하고 양방향 데이터 채널만 역방향으로 전송할 수 있으며 데이터는 슬레이브 끝에서 얻습니다. 완전한 양방향 데이터 채널 모듈(Universal Lane)의 개략도는 다음과 같습니다.

그림 3(MIPI Alliance Specification for D-PHY, Version 2.0)

MIPI D-PHY 채널 트랜시버

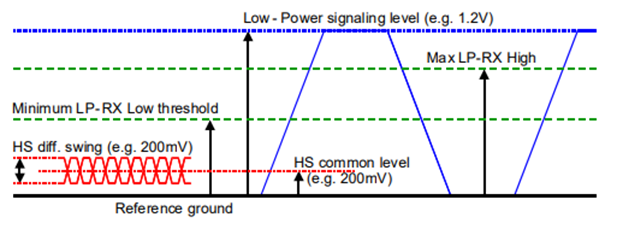

D-PHY 채널은 두 가지 유형의 고속 및 저전력 트랜시버를 갖추고 있습니다. 즉, 고속 송신기(HS-TX), 고속 수신기(HS-RX), 저전력 송신기(LP-TX), 그리고 저전력 수신기(LP-RX)로, 따라서 두 가지 전송 모드를 지원합니다: HS 모드(고속 모드)와 LP 모드(저전력 모드). HS 모드는 저전압 차동 신호를 채택하며 많은 전력을 소비하지만 높은 데이터 전송 속도(80M ~ 4.5Gbps)를 가질 수 있습니다. 반면 LP 모드는 단일 신호를 사용하며 데이터 전송 속도는 낮지만(<10Mbps) 상대적으로 낮은 전력 소비가 가능합니다. HS 신호의 전압 범위는 140mV ~ 270mV이며, LP 신호의 전압은 약 1.2V입니다. 아래 그림에서 볼 수 있습니다. 이 두 모드의 조합으로 D-PHY는 필요할 때 대량의 데이터를 높은 속도로 전송하면서 나머지 시간에는 더 적은 전력을 소비할 수 있습니다.

그림 4(MIPI Alliance Specification for D-PHY, Version 2.0)

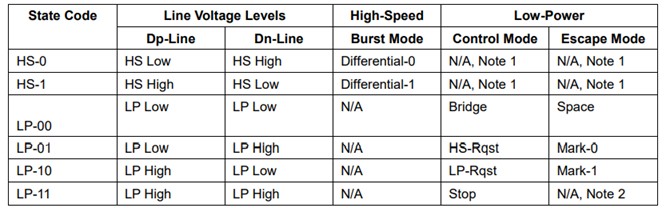

그 중 고속 송신기는 차동 방식으로 채널을 구동하며, 차동-0과 차동-1의 두 가지 채널 상태가 있습니다. 저전력 송신기는 단일 방식으로 두 개의 라인을 독립적으로 구동하므로 아래 표와 같이 LP-00, LP-01, LP-10 및 LP11의 네 가지 채널 상태가 있습니다. LP 모드에서 서로 다른 채널 상태의 조합을 사용하여 전송 신호를 제어하여 서로 다른 동작 모드로 들어갈 수 있으며 이에 대해서는 나중에 자세히 설명하겠습니다.

표 1(MIPI Alliance Specification for D-PHY, Version 2.0)

MIPI D-PHY 동작 모드

D-PHY에는 세 가지 주요 동작 모드가 있습니다: 제어 모드(Control Mode), 연속 모드(Burst Mode) 및 탈출 모드(Escape Mode). 정상 동작 상태에서 데이터 레인은 제어 모드나 고속 모드가 됩니다.

– Control Mode

제어 모드에서 데이터 채널이 전송하는 신호는 LP 신호이며 위에서 언급한 바와 같이 LP-00, LP-01, LP-10 및 LP-11의 4가지 채널 상태가 있습니다. 그 중 고속 모드로 진입하는 순서는 LP-11, LP-01, LP-00이며, 이때 데이터 채널은 정지 상태(LP-11)를 수신할 때까지 고속 모드를 유지한다. 탈출 모드로 들어가는 순서는 LP-11, LP-10, LP-00, LP-01, LP-00입니다. 두 모드는 제어 모드 내의 요청에 의해 입력되어야 합니다.

– Burst Mode

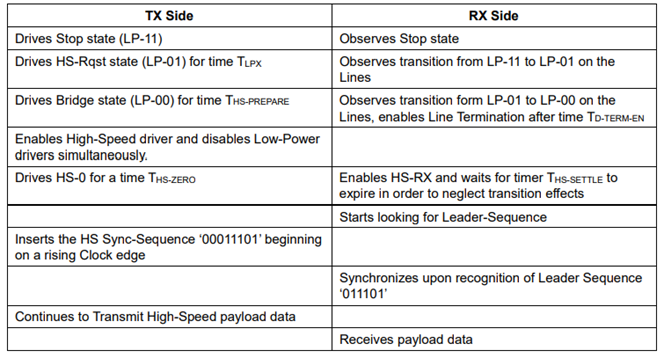

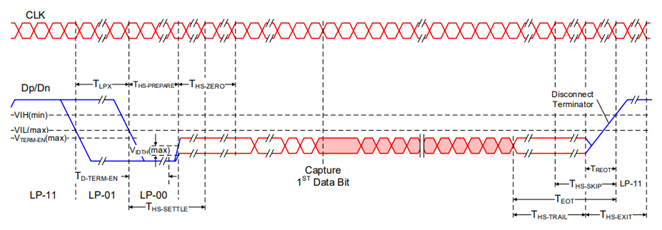

고속 모드에서 고속 데이터 전송은 버스트로 발생하며 정지 상태(LP-11)에서 시작하고 끝납니다. HS 신호 전송을 시작하기 전에 데이터 채널은 정지 상태를 벗어나 전송 시작 절차(Start-of-Transmission)를 통해 고속 모드로 들어갈 준비를 합니다. 표 2에서와 같이 TX와 RX 양측의 이벤트 순서를 각각 설명합니다. LP 신호가 LP-11, LP-01, LP-00의 순서를 차례로 거친 후 RX는 Line Termination을 수행하고 TX는 LP 신호 드라이버를 닫고 동시에 HS 신호 드라이버를 활성화합니다. 데이터 채널이 HS 신호를 전송하는 동안 클럭 채널은 DDR 클럭을 제공하기 위해 고속 모드에 있어야 합니다.

표2(MIPI Alliance Specification for D-PHY, Version 2.0)

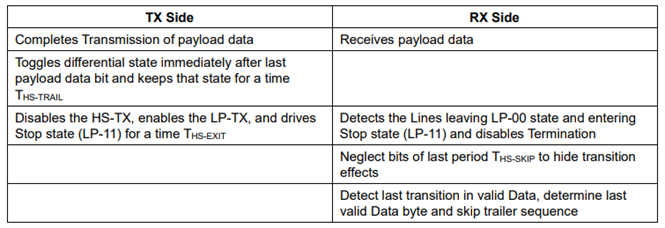

데이터 버스트가 끝나면 데이터 채널은 표 3과 같이 전송 종료 절차(End-of-Transmission)를 통해 정지 상태로 들어갑니다.

표3(MIPI Alliance Specification for D-PHY, Version 2.0)

정상 신호 전송 동안 제어 모드에서 고속 모드로 진입합니다. 이때 HS 신호가 전송됩니다. HS 신호 전송이 완료되면 고속 모드를 벗어나 제어 모드로 돌아갑니다. 전체 데이터 버스트 동안의 이벤트 순서는 아래 그림에 나와 있습니다. 각 채널의 전송은 프로토콜에 의해 독립적으로 시작하고 종료될 수 있으며, 대부분의 경우 채널은 동기적으로 시작하지만 바이트 수가 다른 것으로 인해 종료 시간이 다를 수 있습니다.

그림 5(MIPI Alliance Specification for D-PHY, Version 2.0)

– Escape Mode

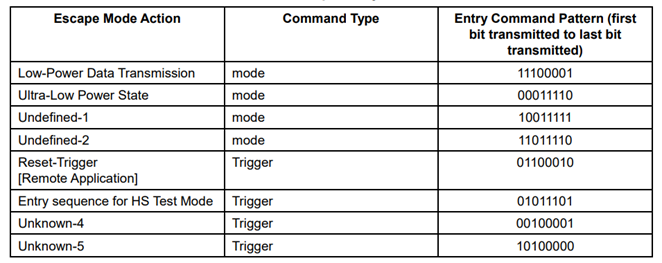

탈출 모드는 데이터 채널이 저전력 상태인 경우에 사용되는 특수한 동작 모드입니다. 예를 들어, 저전력 데이터 전송(Low-Power Data Transmission, LPDT), 초 저전력 상태(Ultra-Low Power State, ULPS), 원격 트리거 등이 해당됩니다. LP 신호가 LP-11, LP-10, LP-00, LP-01, LP-00 순서로 전달되면 데이터 채널은 탈출 모드로 진입하며, 송신기는 요청된 동작을 나타내는 8비트 진입 명령을 보냅니다. 이러한 명령들 중 미할당된 명령들은 향후 확장을 위해 예약되어 있습니다. 정지 조건(LP-11)은 탈출 모드를 종료하고 즉시 제어 모드로 돌아가기 위해 사용됩니다.

표 4(MIPI Alliance Specification for D-PHY, Version 2.0)

이상 MIPI D-PHY의 두 데이터 전송 모드(고속 모드, 저전력 모드)와 세 동작 모드(제어 모드, 고속 모드, 탈출 모드)에 대한 소개였습니다.

References

- MIPI Alliance Specification for D-PHY, Version 2.0, 23 November, 2015

Author

GRL Senior Test Engineer, Nicole Lan

GRL 기술 기사의 저자이자 강사로 4년의 DP 테스트 경험이 있으며 DP, HDR, MIPI 및 기타 인터페이스 테스트에 전문입니다.

이 문서의 사양 및 설명은 사전 통지 없이 변경될 수 있습니다.

Release Date 2021/10/27 AN-211027-TW

/MIPI%20C-PHY%20Overview_featured%20image.png)