DDR 테스트

DDR

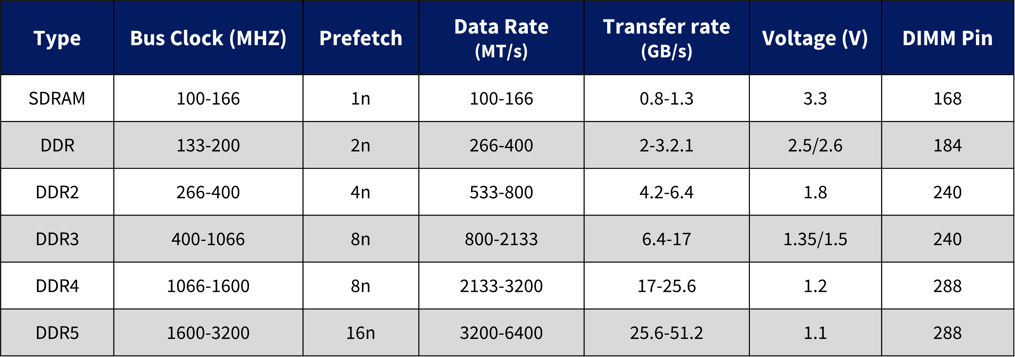

Double Data Rate, DDR은 컴퓨터 및 기타 전자 장치의 성능을 향상시키기 위해 사실상 표준이 된 메모리 기술의 일종입니다. DDR SDRAM(동기식 동적 랜덤 액세스 메모리)은 메모리가 시스템 클럭과 동기화되어 임의의 순서로 모든 메모리 위치에 액세스할 수 있음을 의미합니다. DDR은 수년에 걸쳐 성능과 속도에 대한 증가하는 요구를 충족하기 위해 발전해 왔습니다. DDR 표준의 주요 개정이 있을 때마다 메모리 대역폭은 약 두 배로 증가했습니다.

DDR은 클록 신호의 상승 및 하강 에지 모두에서 데이터를 전송하므로 한 사이클당 두 번(따라서 이름) 전송합니다. DDR 표준은 핀 위치, 전송 속도, 전력 소비량이 다릅니다.

JEDEC 협회

JEDEC 솔리드 스테이트 기술 협회(JEDEC Solid State Technology Association)는 1958년에 설립되었습니다. 마이크로 일렉트로닉스 산업을 선도하는 표준 단체입니다. JEDEC의 주요 목표는 SSD(솔리드 스테이트 스토리지), DRAM, 플래시 메모리 카드, RFID(무선 주파수 식별)와 같은 제품의 생산, 테스트 및 기능 정의를 표준화하는 것입니다. https://www.jedec.org 를 참조하십시오.

최신 버전의 DDR 사양

JEDEC 회원은 이 페이지에서 DDR 사양을 확인할 수 있습니다: https://www.jedec.org/standards-documents

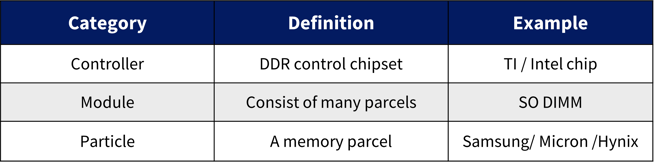

DDR표준 및 명명법

GRL의 DDR 서비스는 일반적으로 DDR 호스트 컨트롤러의 신호 품질 성능을 JEDEC 표준에 따라 검증하는 데 중점을 둡니다.

DDR 테스트 프로세스

DDR 테스트 프로세스

DDR 신호를 프로브하려면 인터포저를 DRAM 구성 요소에 설치해야 합니다. s-파라미터를 사용할 수 있는 경우 인터포저를 제거할 수 있습니다. GRL은 DDR 인터포저를 선택 및 설치할 수 있습니다(비용 청구).

고객이 제공해야 할 것

- 테스트할 각 부품에 대한 정확한 DQ(데이터 비트), DQS(스트로브) 및 A(주소 비트).

- 호스트 컨트롤러 시스템

- DDR 인터포저가 설치된 칩을 대상으로 특정 트래픽을 생성하는 소프트웨어 도구로, 테스트 기간 동안 가능한 한 많은 DQ 및 주소 비트를 실행합니다.

DDR 트래픽 요구사항

- DDR은 무작위 데이터와 8워드 이상의 버스트로만 씁니다. 애플리케이션이 DDR 눈을 구축하려면 버스트 트랜잭션에서 가능한 한 많은 'b0'과 'b1'을 얻기 위해 데이터가 무작위여야 합니다.

DDR5는 모든 트래픽 생성에 대해 최소 200회의 CK 사이클이 필요합니다. - DDR은 무작위 데이터와 8워드 이상의 버스트로만 읽습니다. 스크립트에서 지정된 위치에 무작위 쓰기를 수행한 다음 무한 버스트 읽기를 시작할 수 있습니다.

- 대체 모드의 DDR 쓰기/읽기 버스트는 JEDEC 사양에 대한 테스트에 사용하기에 가장 적합한 트래픽입니다.

DDR 테스트 항목 & 사용 기기

DDR 테스트 항목

DDR 2-3/LPDDR 2-3:

- Set 1 - DQ/DQS Reads and Writes, CS#, and Clock

- Set 2 - Address, CAS#, RAS#, and WE#

DDR 5/DDR 4/LPDDR 4/LPDDR 4x:

- 차등 구성: Clock#, DQS#, DQ-x Reads and Writes, Command (Address-x or CS#)

- (옵션) Single-ended configuration: Clock and/or DQS

LPDDR 5:

- 차등 구성: Clock#, RDQS#, DQ-x Reads and Writes, and WCK#

- (옵션) Single-ended configuration: Clock#, RDQS#, and/or WCK#

- (옵션) Receiver physical layer

테스트 예산은 Write 트랜잭션만(DIMM에서) 또는 Read 트랜잭션만(Host에서)으로 제한하거나 테스트 매트릭스를 줄임으로써 확인할 수 있습니다.

DDR 테스트 장비

- Keysight or Rohde & Schwarz RTP 16GHz real-time oscilloscope

- Differential probes

- DDR conformance test automation software