Signal integrity란?

신호 무결성은 신호가 왜곡 없이 송신기에서 수신기로 전파될 수 있는 정도를 측정합니다. 이동 과정에서 신호를 방해할 수 있는 환경 요인은 다음과 같습니다.

- Crosstalk

- Ground bounce

- Jitter

- Mismatch

- Reflections

- Ringing

인쇄 회로 기판(PCB)에서 신호 무결성이 중요한 이유

신호 무결성에 대한 환경적 영향을 최소화하려면 특별한 주의가 필요합니다. 많은 전자 장치의 필수 구성 요소인 인쇄 회로 기판(PCB)은 절연 유리 섬유 구성 요소와 전도성 구리 금속 트랙으로 만들어진 눈에 띄는 녹색 판입니다. 높은 신호 속도는 종종 PCB에서 병목 현상을 일으키기 때문에 신호 무결성 분석은 신호를 빠르고 안정적으로 전송할 수 있을 때까지 PCB를 설계하고 재구성하는 데 자주 사용됩니다.

Signal integrity 테스트 및 분석

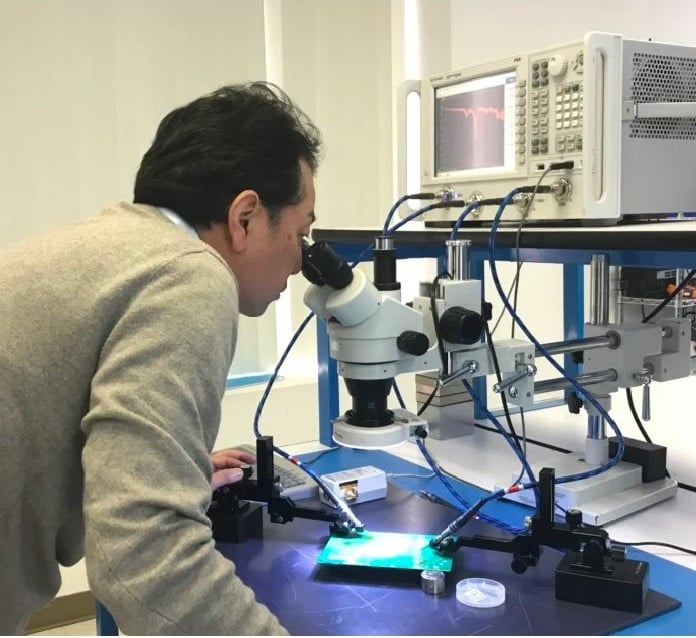

제어된 환경에서 송신기와 수신기 모델 간에 신호를 생성하여 신호 무결성 테스트를 수행할 수 있습니다. 신호 무결성을 분석할 때 다음 요소가 테스트 결과에 영향을 미치지 않도록 하는 것이 중요합니다.

- 신호판에 브리지됨

- DUT(Device Under Test) 용접 각도

- 측정 방법

- 신호 채택 라인 길이

- 주변 요소 간섭

- 테스트 포인트

신호 품질, 누화 및 타이밍을 검사하여 신호 문제의 원인을 좁힐 수 있습니다.

VNA 및 TDR 분석

VNA 및 TDR은 디지털 신호 무결성 측정입니다. VNA는 동기화된 방식으로 송신기와 수신기를 스캔하기 위해 협대역 필터를 통해 사인파를 스윕하여 측정됩니다. 여기에서 주파수 도메인 성능(S-파라미터) 및 시스템 손실(삽입 및 반사 손실)에 대한 정보를 검색할 수 있습니다. VNA 데이터는 DUT 토폴로지에 대한 추가 통찰력을 얻기 위해 추가 소프트웨어를 사용하여 시간 도메인으로 변환되어야 합니다.

TDR은 광대역 등가 샘플링 오실로스코프와 신호를 DUT로 보내는 내부 단계 생성기로 구성된 장비를 사용하여 측정됩니다. TDR 분석을 통해 설계자는 오류 위치, 임피던스, 시간 지연 및 시스템 토폴로지와 같은 DUT 속성을 측정할 수 있습니다. 누화, 상승 시간 저하, 반사 손실, 표피 효과 및 유전 손실과 같은 더 많은 속성도 TDT(시간 도메인 전송)를 사용하여 측정할 수 있습니다. 이 측정 기술의 일시적 특성으로 인해 TDR 결과는 시각적이고 직관적입니다. 주파수 종속 행동 관찰에는 일반적으로 추가 소프트웨어가 필요합니다.

Power integrity란?

전원 무결성은 드라이버와 수신기를 통해 흐르는 전류를 나타냅니다. 신호를 안정적으로 송수신하려면 이 전류가 안정적으로 유지되어야 합니다. 따라서 전력 무결성은 신호 무결성의 하위 집합으로 간주될 수 있습니다. 신호 무결성과 전력 무결성은 모두 디지털 회로 내에서 적절한 아날로그 작동에 필수적입니다.

전력 무결성 문제는 주로 전압 리플 잡음에서 비롯되며, 과도 전류가 채널 인덕턴스와 반응할 때 생성됩니다. AC 소스가 DC 레일로 변환될 때 과도 전류가 차례로 생성됩니다. 모든 구성 요소가 주 전원 공급 장치에 연결되어 있기 때문에 리플 노이즈가 누화를 통해 시스템의 모든 부분으로 전달되어 영향을 미칠 수 있습니다.

필터링되지 않은 AC 전원에서 발생하는 전자기 간섭(EMI)은 전원 무결성 중단의 또 다른 일반적인 원인입니다. 적절한 설계가 없으면 EMI는 무선 신호에 영향을 미치고 규정 준수를 위한 EMC(전자파 적합성) 테스트 중에 혼선을 유발할 수 있습니다.

Power integrity 테스트 및 분석

전원 무결성 분석에는 장치가 의도한 대로 작동하도록 장치를 통해 충분한 전류가 안정적으로 전송될 수 있도록 DC 전원 레일 중단 및 EMI 문제 식별이 포함됩니다.

전력 무결성 테스트를 위한 매개변수는 신호 무결성 구성 요소에 따라 달라지므로 정의하기 어려울 수 있습니다. 또한 더 높은 주파수 에너지는 전송 평면을 통해 분산될 때 x 및 y 방향 모두로 이동하여 분석 복잡성을 더욱 가중시킵니다.

DC 레벨에서의 분석에는 트레이스, 평면 모양 및 비아의 직렬 저항만 계산하면 되지만 보드 위치, 장착 방법, 커패시터의 위치, 유형 및 값과 같은 추가 요소는 더 높은 주파수에서 고려해야 합니다.

PCB 설계 가이드

Via

Via는 보드의 표면 레이어를 내부 및 외부 레이어 모두로 추적하는 데 사용되는 PCB의 도금 관통 구멍입니다. PCB 비아는 전기 연결을 생성하기 위해 기계적으로 뚫고 도금할 수 있으며 다음 구성 요소로 구성됩니다.

- Barrel: 여과된 구멍을 채우는 전도성 튜브.

- Pads: 배럴 끝을 트레이스에 연결합니다.

- Antipads: 배럴과 비연결 레이어를 분리하는 클리어런스 홀.

다층 기판에서 Via는 Via 크기와 유형에 따라 달라지는 전류량과 함께 층 사이의 전기 및 열 전류 흐름을 위한 경로를 생성합니다. Via 유형에는 다음이 포함됩니다.

- Through-hole via: Via의 가장 일반적인 유형

- Blind via: PCB의 다른 부분에서는 볼 수 없습니다. 보드의 표면 레이어를 후속 레이어에 연결하는 데 사용됩니다.

- Buried via: PCB의 표면에서 볼 수 없습니다. 보드의 내부 레이어를 연결하는 데 사용됩니다.

Layer stacking

PCB 레이어 스태킹은 신호 무결성을 결정하는 데 중요한 역할을 합니다. 신중한 레이어 구성은 공통 모드 전류를 생성하는 임피던스를 방지하여 RF 에너지를 생성합니다. RF 에너지가 전력 분배 네트워크 또는 여유 공간에 들어가면 신호 방해 반사, 링잉 또는 누화를 생성하는 노이즈를 방출합니다.

반대로 적절한 PCB 레이어 스태킹은 신호 무결성을 유지하는 데 도움이 되는 기능을 통합할 수 있습니다. 예를 들어, 인접한 접지판으로 차폐 및 내부 레이어 플럭스 상쇄를 최대화하기 위해 고속 트레이스를 스트립라이닝할 수 있습니다. 덜 민감한 트레이스는 공기를 통한 결합 위험이 낮기 때문에 외부 PCB 레이어에 마이크로스트라이핑될 수도 있습니다.

Trace routing

트레이스 라우팅은 Via 및 레이어 스태킹이 완료된 후에 이루어지며 PCB 구성 요소의 위치와 밀접하게 연결되어 있습니다. 예를 들어 모든 신호가 연결되고 바이패스 캡과 같은 관련 구성 요소가 해당 핀에 최대한 가까이 있도록 이스케이프 라우팅을 신중하게 설계해야 합니다.

일반적인 추적 라우팅 모범 사례는 다음과 같습니다.

- 항상 신호 경로 추적을 가능한 한 짧고 직선적으로 유지하십시오.

- 아날로그 또는 전원 공급 장치 섹션과 같이 복잡한 회로 부분을 통해 민감한 신호를 라우팅하지 마십시오.

- 필요할 때마다 특정 라우팅 토폴로지를 위한 충분한 공간을 남겨둡니다.

- 앞으로 더 많은 신호 무결성 문제를 일으킬 수 있는 길이와 인덕턴스를 피하기 위해 비아를 최소화합니다.

- 클록 라인과 같은 민감한 고속 신호를 다른 트레이스에서 가능한 한 멀리 분리합니다. 트레이스 폭의 최소 3배를 사용해야 합니다.

- 서로 단단히 연결된 차동 쌍을 묶고 비아와 같은 장애물 주변에서 쌍을 나누지 마십시오.

- 길이가 같아야 하는 네트 그룹을 라우팅할 때마다 가장 긴 연결부터 시작하여 모든 네트가 동일한 길이에 도달할 때까지 나머지에 튜닝 턴을 추가합니다.