Granite River Labs, GRL

Wing Tseng 曾威華

在 USB3.2 的規範中,分為物理層 (Physical Layer)、鏈路層 (Link Layer) 以及協議層 (Protocol Layer) 三大類型測試。物理層代表著訊號傳送與接收的好壞,鏈路層為確保兩個鏈路夥伴 (Link Partner) 成功溝通帶有信息的傳輸數據包,協議層則確保鏈路層上的數據包能正確傳輸。

數據包類型分為四種:

- Link Management Packet (LMP)

- Transaction Packet (TP)

- Data Packet (DP)

- Isochronous Timestamp Packet (ITP)

通常在物理層測試之後,接著需要測試 USB 的鏈路層,本篇文章我們將會介紹 USB3.2 Link Layer 測試項目。

USB3.2 Link Training and Status State Machine (LTSSM)

進入鏈路層測試的介紹前,我們先認識 USB3.2 的 LTSSM,LTSSM 是 USB3.2 在訊號溝通之後可能的鏈路狀態流程圖,USB3.2 LTSSM 如下圖所示 。

.png?width=259184&name=%E5%9C%96%E7%89%873-1%20(1).png)

圖 1

(取自 Universal Serial Bus 3.2 Specification)

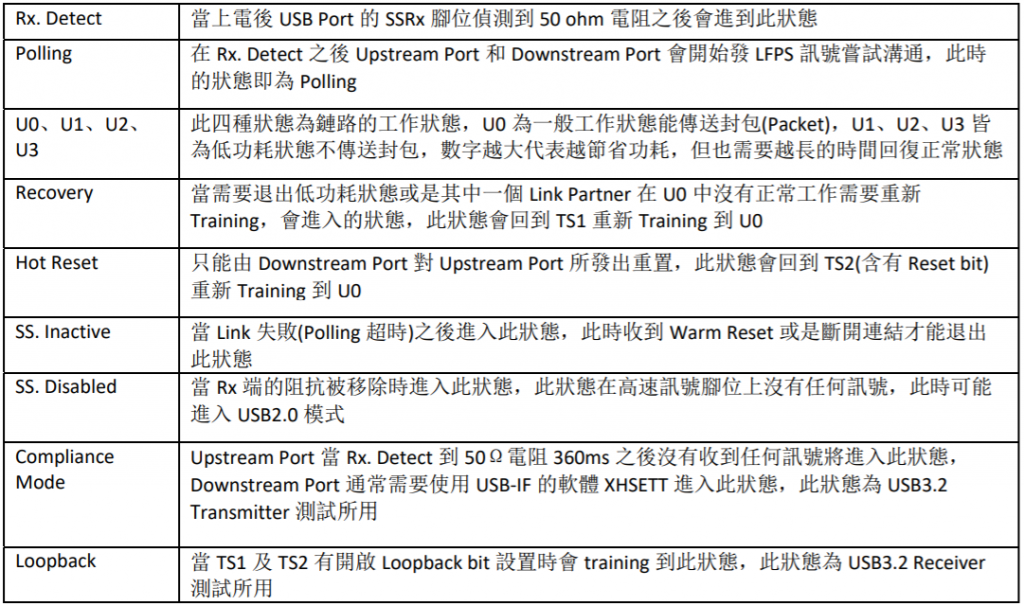

下表則為 LTSSM 各種狀態的介紹:

表 1

USB3.2 Polling Substate Machine

有了 LTSSM 的認識之後,換介紹 USB3.2 Polling 子狀態,圖二為 Polling Substate Machine,可從圖中了解到 USB3.2 Gen2 的 Polling 溝通訊號順序為:

SCD1 → SCD2 → LBPM PHY Capability → LBPM PHY Ready → TSEQ → TS1 → TS2

另外也講述 USB3.2 Gen1 的 Polling 溝通訊號順序為:

LFPS → TSEQ → TS1 → TS2

所以我們發現 SCD1 及 SCD2 和 LBPM 系列是 USB3.2 Gen2 才新增的一種 LFPS 溝通訊號。舉例來說,對照圖二即可知道當 Link Partner 溝通 SCD2 完畢,Polling Substate 會進入 Polling.PortMatch 狀態,其他依此類推。

.png?width=226150&name=%E5%9C%96%E7%89%874-1%20(1).png)

圖 2

(取自 Universal Serial Bus 3.2 Specification)

USB 3.2 鏈路層測試(Link Layer Test)

有了上面的認識之後,我們可以開始介紹 Link Layer 測試。在測試項目中分有 TD6.X 和 TD7.X 部分,兩者皆屬於 USB 的鏈路層測試部分,TD6.X 的測項較偏物理層的延伸測試,TD7.X 屬於鏈路層測試。

以下我們將逐一介紹每一個測試項目,其中 Link Validation System (LVS) 指鏈路驗證系統,目前最常作為 LVS 測試儀器為 LeCroy M310P。

TD6.1 Lane Polarity Inversion Test

LVS 將 SSTx+及 SSTx‐做一個顛倒反向去與 PUT 進行溝通,PUT 能夠順利溝通進入到 U0 即為 Pass, Port Under Test (PUT) 則是指待測接口。

TD6.2 SKP Test

此測項是測 PUT 能夠支援所有可能遇到的 SKP 組合,且能夠順利 training 進入 U0 並維持 50ms。

SKP 為 Skip Ordered Set 其來由是因為在 USB3.2 的高速傳輸下規範必須要有 SSC 展頻時脈,Link Partner 在 SSC 的關係下會造成雙方的傳輸與接收的 Data Rate 不一致,所以需要使用 SKP 來補足 Link Partner 因 SSC 造成的空檔時間。

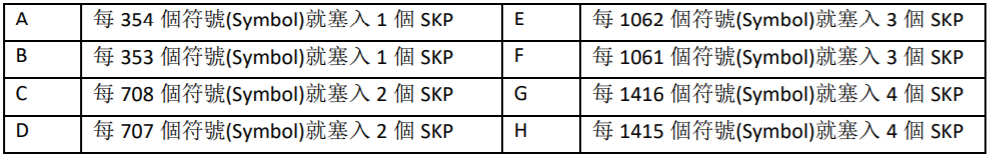

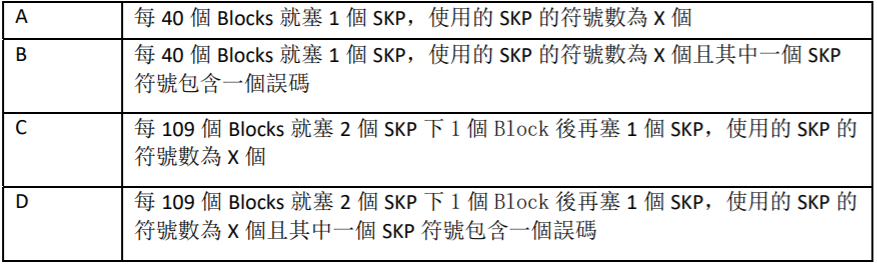

測試方式為 LVS 在 LFPS 溝通之後到 U0 之前,會在 TS1 以及 TS2 結尾部分塞入 SKP,塞入規則 Gen1 和 Gen2 不同,請參考表二與表三:

Gen1 PUT 有八組測試:

表 2

Gen2 PUT 有四組測試:

表 3

若 PUT 沒有 Re‐Timer,X = {4, 8, 12, 16, 20, 24, 28, 32, 36}

若 PUT 有 Re‐Timer,X = {8, 12, 16, 20, 24, 28, 32}

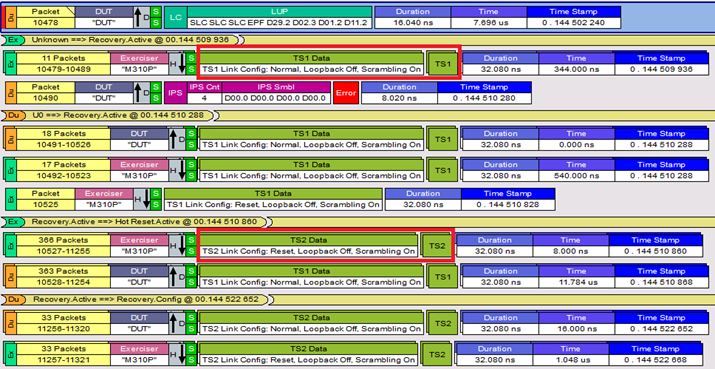

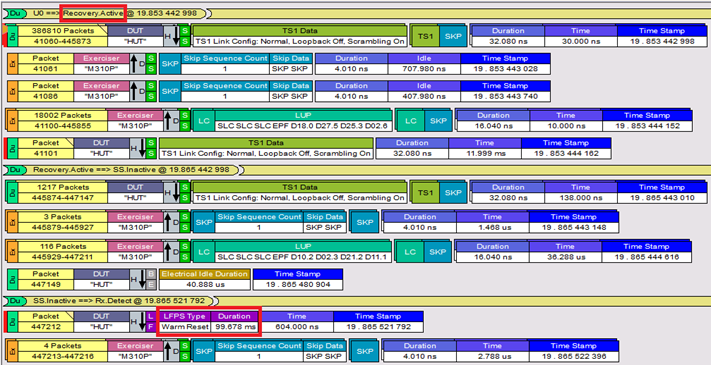

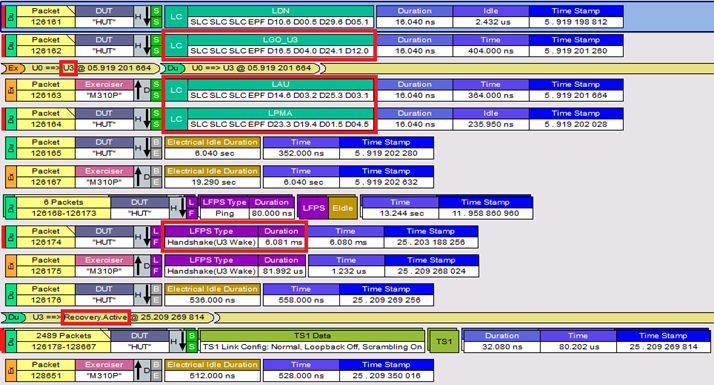

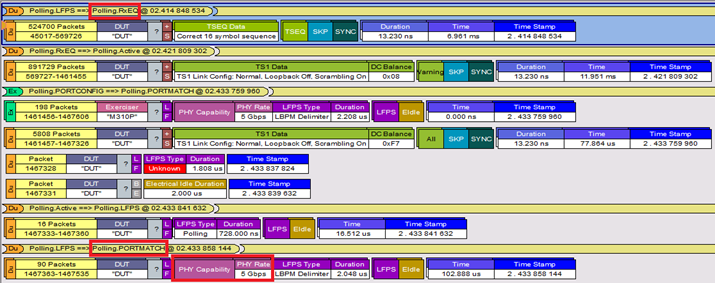

例如圖三為 Gen1 的第 C 組測試 Trace,可看見 LVS 在 TS1 和 TS2 的部分依照規則塞入 SKP,然後成功和 PUT 溝通進入 U0 維持 50ms,所以此測項為 Pass。

.png?width=494656&name=%E5%9C%96%E7%89%875-1%20(1).png)

圖 3

TD6.3 Elasticity Buffer Test

此為 PUT 的傳輸速度緩衝測試,LVS 會模擬 ‐5300ppm 以及 300ppm 的 SSC 訊號與 PUT 溝通,PUT 能夠順利進入 U0 即為 Pass。

TD6.4 LFPS Frequency Test

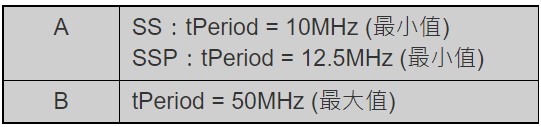

在 USB3.2 中,開始傳輸資料之前會先使用 LFPS 來與 Link Partner 溝通,所以需要測試 LFPS 在規範範圍內的不同頻率下是否還能順利的溝通下去。LFPS 頻率測試分為兩組如表四:

表 4

首先 LVS 第一組用頻率最慢的 LFPS (10MHz) 測試,第二組 LVS 則用頻率最快 (50MHz) 的 LFPS 去做測試。PUT 要能夠在兩組不同頻率的 LFPS 順利溝通進到 Polling.RxEQ 子狀態即為 Pass。

下表為 LFPS 的規範 tPeriod 範圍,即可明白為何此測項定義的最快頻率以及最慢頻率是這個數字。

.png?width=536047&name=%E5%9C%96%E7%89%877%20(2).png)

表 5

(取自 Universal Serial Bus 3.2 Specification)

圖四舉例 Pass 的第一組測試,第一個紅框為 PUT 與 LVS 溝通發送的 LFPS,接下來 LVS 用最慢頻率的 LFPS (10MHz) 回 PUT,第二個紅框看見 PUT 仍然有 LFPS 回 LVS,最後第三個紅框表示 PUT 和 LVS 順利溝通進入 Polling.RxEQ。

.png?width=357429&name=%E5%9C%96%E7%89%876-1%20(1).png)

圖 4

TD6.5 Polling.LFPS Duration Test

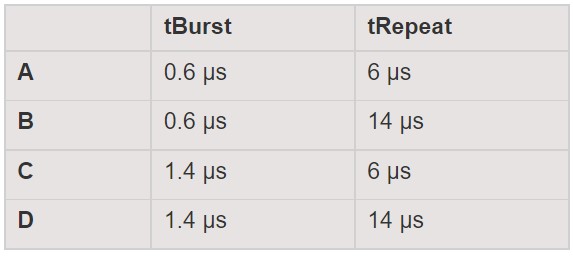

在 TD6.5 測試 LVS 用 Polling.LFPS 在規範範圍內的最大與最小的 tBurst 和 tRepeat 與 PUT 溝通要能夠順利進入 Polling.RxEQ。

此測項分有四組測試如表六:

表 6

測試值一樣可以從 USB3.2 的 Polling.LFPS 規範如表七中得到:

.png?width=539967&name=%E5%9C%96%E7%89%878%20(1).png)

表 7

(取自 Universal Serial Bus 3.2 Specification)

TD6.6 SCD Duration Test (Gen2 Capable Only)

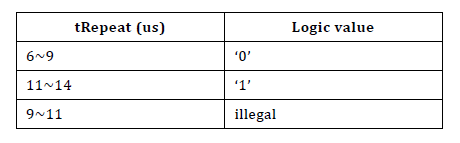

USB 3.2 Gen2 的 LFPS 使用 SCD1 及 SCD2 來溝通,與 Gen1 的差別只在於 tRepeat 的時間長短被改變了,SCD 的規範如表八。SCD1 定義為邏輯上的“0010”,SCD2 則定義為邏輯上的“1101”。

表 8

(取自 Universal Serial Bus 3.2 Specification)

接下來就用一樣的原理,LVS 使用在規範內最大與最小數值的 SCD 訊號與 PUT 溝通,然後能夠順利進入到 Polling.PortMatch 即為 Pass,LVS 測試使用八組如下表:

表 9

TD6.7 PWM Duration Test (Gen2 Capable Only)

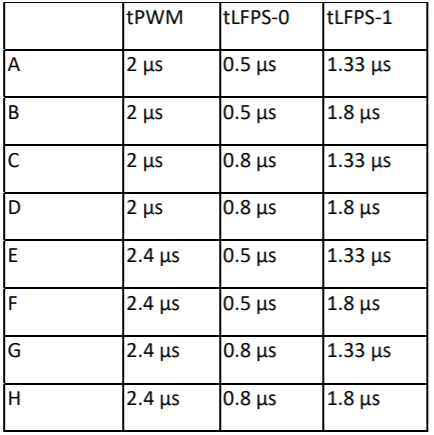

USB 3.2 在 SCD 訊號溝通完之後會換使用 LBPM 來溝通,LBPM 是 LFPS 去做脈衝長度調變的一種訊號,LBPM 的規範如表十:

-1.png?width=1087753&name=%E5%9C%96%E7%89%8710%20(1)-1.png)

表 10

(取自 Universal Serial Bus 3.2 Specification)

使用同 TD6.6 的原理,LVS 用最大與最小數值的 LBPM 去跟 PUT 溝通要能夠順利進入 Polling.RxEQ 即為 Pass,LVS 測試使用八個組合如表十一:

表 11

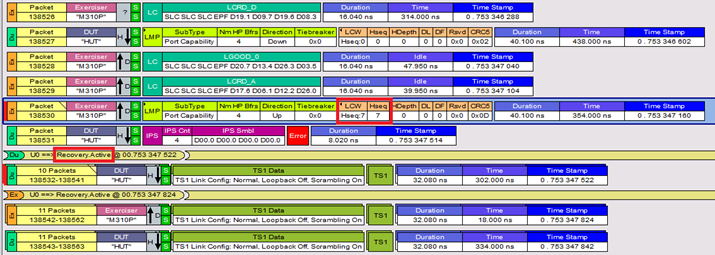

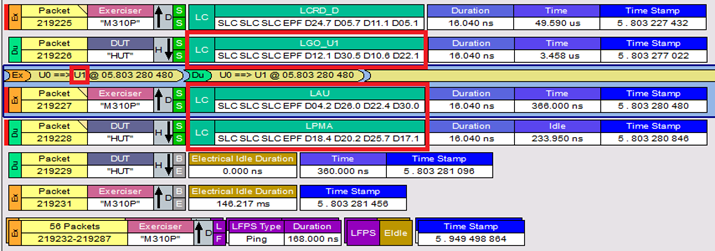

TD7.1 Link Bring‐up Test

此測項要確保 PUT 與 LVS 的溝通能夠順利進到 U0 且溝通的訊號數量也都符合規範。其中又分為五個子測項,若為 Gen1 的 PUT 要測子測項 1 及 2,有 Gen2 的 PUT 要再多測子測項的 3、4 和 5。

-子測項 1:TD7.1.1 模擬 Gen1 的 LVS 與 Gen1 的 PUT 溝通

- LVS 等待 PUT 的 Polling.LFPS

- LVS 收到之後發送 4 個 Polling.LFPS

- PUT 沒有 Re‐timer 至少連續發送 16 個 Polling.LFPS;若有 Re‐Timer 至少連續發送 4 個 Polling.LFPS。當 PUT 收到 1 個 Polling.LFPS 時,至少要連續發送 4 個 Polling.LFPS 但不可超過 6

- 接著開始 TSEQ 的 Training,LVS 會發 65536 個 TSEQ,PUT 也要回 TSEQ 但中間不可包含 SKP 和 Idle 符號以及任何封包、符號和 Ordered Set

- 然後是 TS1 Training,LVS 等待連續 8 個的 TS1 或 TS2,在 TS1 指令集傳送的中途不可有 SKP 打斷

- 最後進入 TS2 Training,PUT 收到 1 個 TS2 之後連續回傳 16 個 TS2,在 TS2 指令集傳送的中途不可有 SKP 打斷

- 最後 PUT 和 LVS 雙方進入 U0

-子測項 2:TD7.1.2 模擬 Gen2 的 LVS 與 Gen1 的 PUT 溝通

- LVS 發送 SCD1

- 沒有 Re‐Timer 的 PUT 要連續發送至少 16 個 Polling.LFPS

- LVS 發送 4 個 SCD1 及收到 16 個 Polling.LFPS 之後要改為發送 Polling.LFPS

- 接著 PUT 要連續發送至少 4 個 Polling.LFPS 但不可超過 6 個

- 最後接續 TD7.1.1 的第 4 步驟

-子測項 3:TD7.1.3 模擬 Gen1 的 LVS 與 Gen2 的 PUT 溝通

- LVS 發送 16 個 Polling.LFPS

- PUT 在收到 LVS 的 16 個 Polling.LFPS 及發送 4 個 SCD1 之後改發 Polling.LFPS

- 沒有 Re‐Timer 的 PUT 要發送 16 個 Polling.LFPS

- 在收到 LVS 的 1 個 Polling.LFPS 後,PUT 要連續發送 4 個 Polling.LFPS

- PUT 沒有 Re‐Timer 發送 16 個 Polling.LFPS 之後要進 Polling.RxEQ;若有 Re‐Timer 則是發送 4 個 Polling.LFPS 之後要進 Polling.RxEQ

- 最後接續 TD7.1.1 的第 4 步驟

-子測項 4:TD7.1.4 模擬 Gen2 的 LVS 與 Gen2 的 PUT 溝通

- LVS 發送 SCD1

- PUT 在收到 1 個 SCD1 或 SCD2 之後發送 2 個 SCD1

- LVS 在發送 2 個 SCD1 及收到 1 個 SCD1 或 SCD2 之後發送 SCD2

- PUT 在收到 1 個 SCD2 之後發送 2 個 SCD2

- PUT 在收到 2 個連續 PHY Capability 或 PHY Ready 之後發送 3 個連續 PHY Capability

- LVS 發送 524288 個 TSEQ,TSEQ 每 16384 個 Ordered Sets 塞入 SYNC

- PUT 也回送 TSEQ,TSEQ 每 16384 個 Ordered Sets 塞入 SYNC 且中間不可包含 SKP 和 Idle 符號以及任何封包、符號和 Ordered Set

- LVS 發送 TS1,TS1 每 32 個 Ordered Sets 塞入 SYNC,如有需要也可加入 SKP

- LVS 要收到 PUT 的連續 8 個相同的 TS1 或 TS2

- LVS 連續發送 8 個相同的 TS1 或 TS2 之前 PUT 發送 TS2,在 TS1 訓練的中途不可有 SKP 或 SYNC 打斷

- LVS 發送 TS2,TS2 每 32 個 Ordered Sets 塞入 SYNC,如有需要也可加入 SKP

- PUT 在收到 1 個 TS2 之後發送連續 16 個 TS2,在 TS2 訓練的中途不可有 SKP 或 SYNC 打斷

- LVS 發送連續 8 個 TS2 之前 PUT 發送 Idle 符號,接著 LVS 發送 1 個 SDS 和含有 Data Blocks 的 Idle 符號

- 最後 PUT 和 LVS 雙方進入 U0

-子測項 5:TD7.1.5 模擬 Gen1 的 LVS 與 Gen2 的 PUT 溝通 (有別於 TD7.1.3 這次是等待 PUT 先發送)

- LVS 等待 PUT 的 SCD1

- LVS 發送 Polling.LFPS 然後進入 Polling.RxEQ

- PUT 要改發送 Polling.LFPS 降到 Gen1 然後進入 Polling.RxEQ

- 最後接續 TD7.1.1 的第 4 步驟

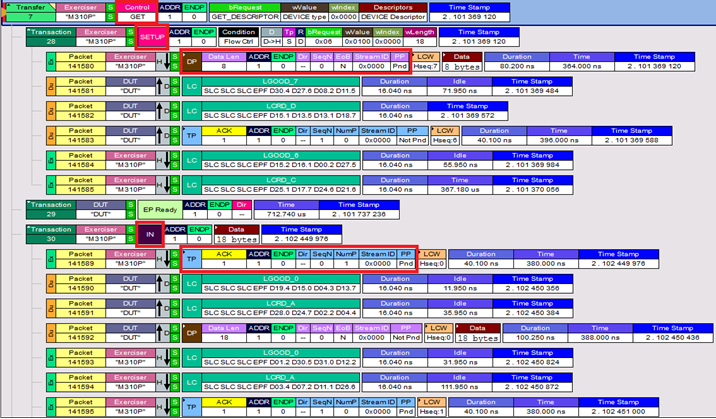

TD7.2 Link Commands Framings Robustness Test

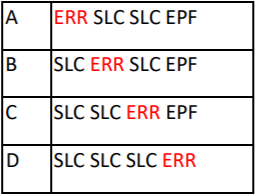

Link Command 中的前四組符號稱為 LCSTART,LCSTART 由三個 SLC 和一個 EPF 所組成。在溝通上要能夠容忍 LCSTART 有一個符號的錯誤,所以此測項 LVS 使用含有一個 ERR 符號的 LCSTART 與 PUT 溝通,能夠進入 U0 維持 50ms 為 Pass。分為四組測試如下表:

表 12

圖五為 A 組測試的範例,可看見紅框中 LVS 發送了一組 Link Command 在 LCSTART 第一個符號是一個錯誤符號,但 PUT 還是能夠與 LVS 繼續溝通下去進入 U0。

.png?width=345787&name=%E5%9C%96%E7%89%8711%20(1).png)

圖 5

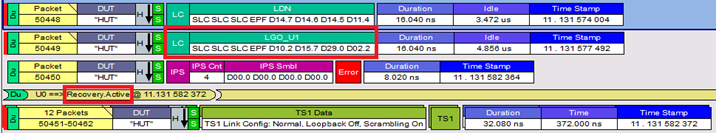

TD7.3 Link Commands CRC‐5 Robustness Test

Link Command Word (LCW) 為 2 個 Bytes,最後 5 個 bits 為 CRC‐5。在測試中 LVS 也會使用錯誤的 CRC‐5 與 PUT 溝通。測試組合分為三組。

Gen1 在組合 A、B 及 C 都要 Recovery 重新 training,但在 Gen2 的部分組合 A 及 B 可以容忍錯誤繼續溝通進入 U0 並維持 50ms,組合 C 則也是要 Recovery 重新 training 才算 Pass。

.png?width=524419&name=%E5%9C%96%E7%89%8712%20(2).png)

圖 6

圖六為 Gen1 的測試組合 A 範例,可從紅框中發現 LVS 使用第一個 CRC‐5 為錯誤來與 PUT 溝通,PUT 也進入 Recovery 重新 training。

TD7.4 Invalid Link Commands Test

此測項發送 Link Commands 其中第一個 LCW 與第二個 LCW 為不相同的指令,但皆有正確的 CRC‐5。LVS 發送第一個 LCW 為 LGO_U1 與第二個 LCW 為 LGO_U2,PUT 不能夠回復 LAU 或 LXU 給這樣的 Link Commands。

當 PUT 收到兩個不同的 LCW 要忽視這兩個指令,繼續 training 進入 U0 並維持 50ms 即為 Pass。

.png?width=484987&name=%E5%9C%96%E7%89%8713%20(1).png)

圖 7

圖七為此測項範例,可從紅框看見 LVS 發送一個 Unknown 的 Link Commands 與 PUT 溝通,此 Link Commands 為圖中下半部顯示,第一個 LCW 與第二個 LCW 不相同。

TD7.5 Header Packet Framing Robustness Test

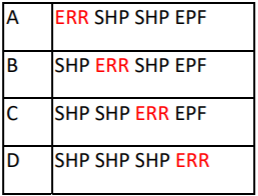

Header Packet 最前面四個 Bytes 稱為 HPSTART,HPSTART 由三個 SHP 和一個 EPF 組成。在溝通上要能夠容忍 HPSTART 有一個符號的錯誤,所以此測項 LVS 使用含有一個 ERR 符號的 HPSTART 與 PUT 溝通,能夠進入 U0 維持 50ms 為 Pass。分為四組去測試如表十四:

表 13

圖八為測試組合 A 的範例,第一個紅框為 LVS 發送含有一個錯誤符號的 HPSTART 的 Header Packet,第二個紅框表示 PUT 可容忍此錯誤符號訓練進入 U0。

.png?width=352833&name=%E5%9C%96%E7%89%8714%20(1).png)

圖 8

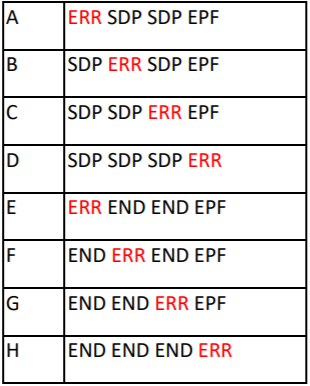

TD7.6 Data Payload Packet Framing Robustness Test

Data Payload Packet(DPP)前四組符號為 DPPSTART,結尾四組符號為 DPPEND。DPPSTART 由三個 SDP 及一個 EPF 組成,DPPEND 由三個 END 及一個 EPF 組成。在溝通中可容忍一個錯誤符號在 DPPSTART 或 DPPEND 裡進入 U0 維持 50ms 即為 Pass,所以測試組合有八組如表十五:

表 14

圖九為 Gen1 的 Downstream Port 測試組合 A 範例,可看見第一個紅框為 LVS 發含有一個錯誤符號的 DP 封包,接著第二個紅框可知 PUT 容忍一個錯誤符號繼續溝通進入 U0。

.png?width=434283&name=%E5%9C%96%E7%89%8715%20(1).png)

圖 9

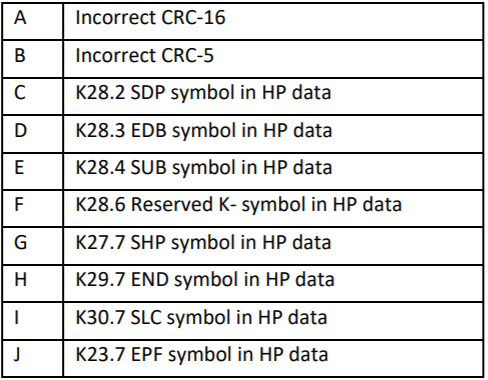

TD7.7 Rx Header Packet Retransmission Test

當 PUT 收到無效的 Header Packet 時,PUT 要回送 LBAD 接著 LVS 回 LRTY 並重新發送正確的鏈路指令繼續溝通到 U0 維持 50ms 為 Pass。測試組合模擬出十種含有錯誤訊息的 Header Packet 來測試 PUT 如下表:

表 15

其中 C 到 J 為 Gen1 才需要測試的組合,且會將錯誤的符號放在兩個不同位置各測試 PUT 一次:

1) 位置 2:SHP SHP SHP EPF DX.X KX.X DX.X DX.X

2) 位置 5:SHP SHP SHP EPF DX.X DX.X DX.X DX.X KX.X

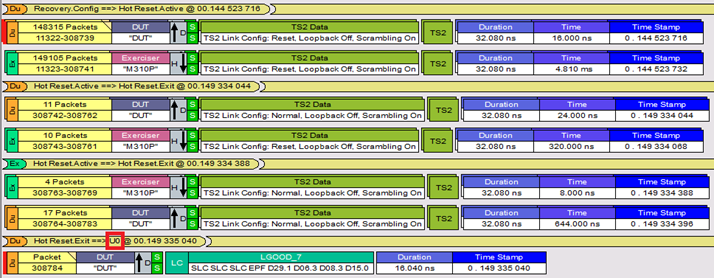

圖十為 Downstream Port 的 Gen1 組合 A 測試範例,可從 Trace 看見第一到第四個紅框為 LVS 發一個含有錯誤CRC‐16 的 HP,PUT 回傳 LBAD,LVS 再回傳 LRTY 並再一次發送正確的 LMP 與 PUT 溝通,最後第五個紅框 PUT 順利溝通進入 U0。

.png?width=349027&name=%E5%9C%96%E7%89%8716%20(1).png)

圖 10

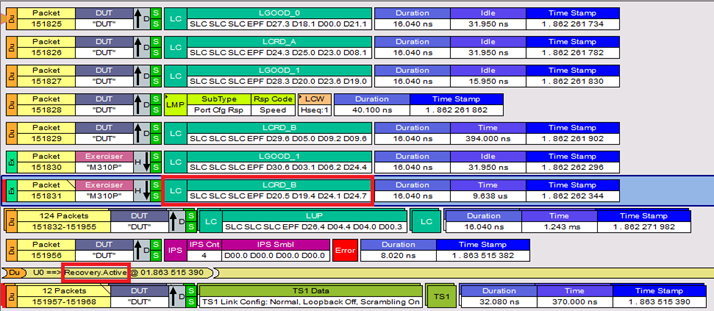

TD7.8 Tx Header Packet Retransmission Test

此測項測試 PUT 在收到 LVS 的 LBAD 時,能夠回送 LRTY 然後重新再發送一次 LMP 與 LVS 溝通進入 U0 維持 50ms 即為 Pass。

所以與 TD7.7 相比發現,TD7.7 為 PUT 接收到 LRTY 的測試,TD7.8 為 PUT 發送 LRTY 的測試。

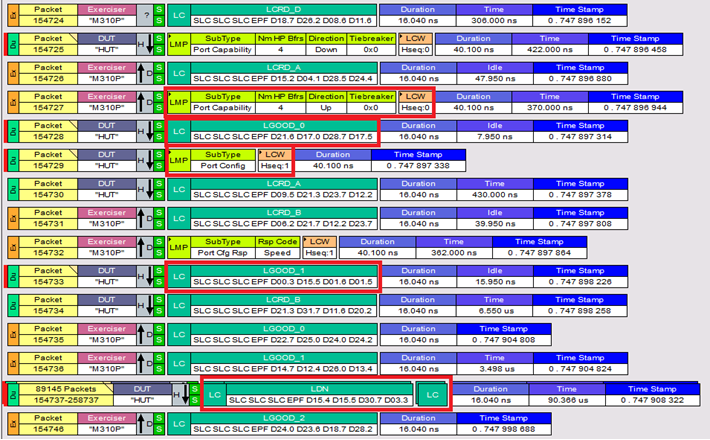

圖 11

圖十一為 Upstream Port 的 Gen1 測試範例,第一到第三個紅框為 LVS 故意發送 LBAD 給 PUT,接著 PUT 有順利的回傳 LRTY 並且再次發送一個 LMP 與 LVS 溝通,最後第四個紅框為 PUT 順利溝通進入 U0。

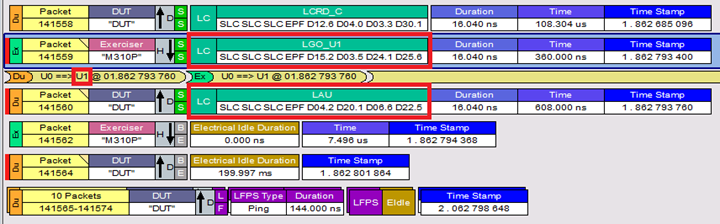

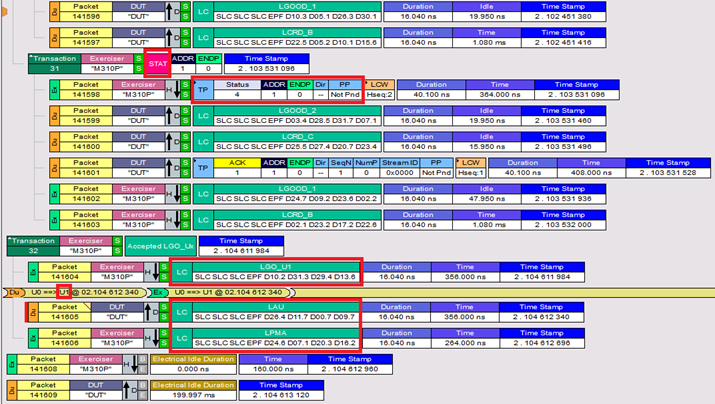

TD7.9 PENDING_HP_TIMER Deadline Test

此測項 PUT 要能夠在 PENDING_HP_TIMER 超時之前回傳 LGOOD_N。

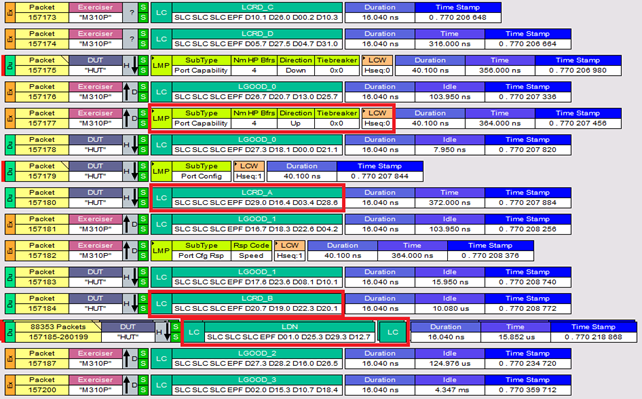

下圖為 Gen1 的 Downstream Port 範例,依紅框順序首先 LVS 在 PENDING_HP_TIMER 超時之前的 200ns 以內 PUT 要能夠回傳 LGOOD 給 LVS 的 Port Capability LMP,接著繼續溝通進入 U0,最後要在 U0 維持 50ms 即為 Pass。

圖 12

TD7.10 CREDIT_HP_TIMER Deadline Test

此測項 PUT 要能夠在 CREDIT_HP_TIMER 超時之前回傳 LCRD_X。圖十三為 Gen1 的 Downstream Port 範例,可從紅框得知在 U0 時,在 CREDIT_HP_TIMER 超時之前的 tLinkTurnAround 時間以內 PUT 要能夠回傳 LCRD 給 LVS 的 Port Capability LMP,接著繼續溝通進入 U0,最後要在 U0 維持 50ms 即為 Pass。

圖 13

TD7.11 PENDING_HP_TIMER Timeout Test

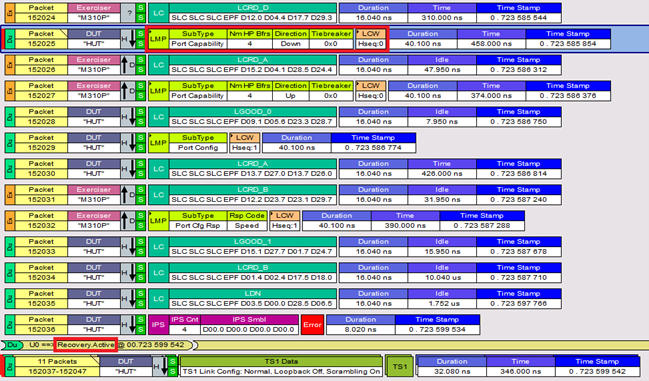

在 PENDING_HP_TIMER 超時之後 PUT 要進入 Recovery 即為 Pass。圖(十四)為測試 Gen1 的 Downstream Port 範例,第一個紅框開始 PENDING_HP_TIMER,之後 LVS 發送 Port Capability LMP 與 PUT 溝通但是直到 PENDING_HP_TIMER 超時都不發送 LGOOD 給 PUT,第二個紅框可看見 PUT 進入 Recovery,表示 PUT 通過了此測項。

圖 14

TD7.12 CREDIT_HP_TIMER Timeout Test

在 CREDIT_HP_TIMER 超時之後 PUT 要進入 Recovery 即為 Pass。圖十五為測試 Gen1 的 Downstream Port 範例,第一個紅框開始 CREDIT_HP_TIMER,之後 LVS 直到 CREDIT_HP_TIMER 超時都不發送 LCRD_X 給 PUT,第二個紅框可看見 PUT 進入 Recovery,表示 PUT 通過了此測項。

圖 15

TD7.13 Wrong Header Sequence Test

此測項為 PUT 收到一個錯誤的 Header Sequence 要進入 Recovery 即為 Pass。

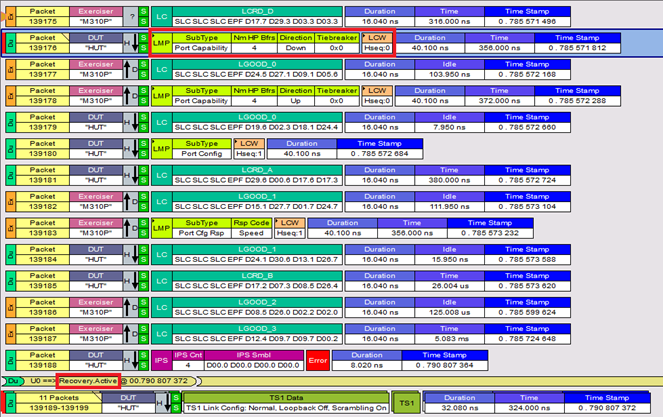

圖十六為 Gen1 的 Downstream Port 範例,可從第一個紅框看見 LVS 發送一個錯誤的 Header Sequence Number,第二個紅框處 PUT 有順利進入 Recovery 代表此測項為 Pass。

圖 16

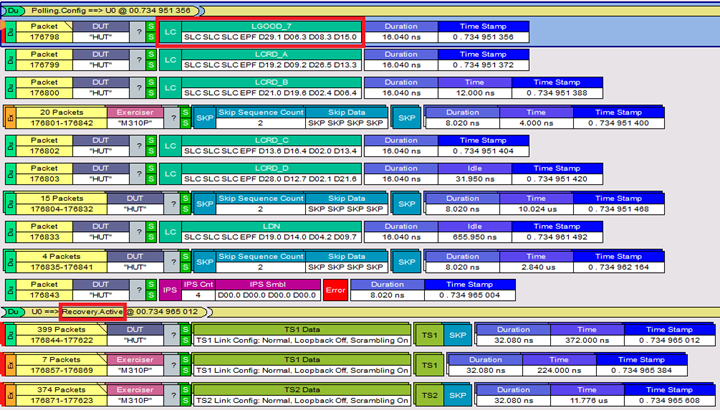

TD7.14 Wrong LGOOD_N Sequence Test

此測項為 PUT 收到一個錯誤的 LGOOD_N sequence 要進入 Recovery 即為 Pass。圖十七為 Gen1 的 Downstream Port 範例,可從第一個紅框看見 LVS 發送一個 LGOOD_7,第二個紅框處 LVS 發送一個錯誤順序的 LGOOD_2,最後 PUT 在第三個紅框有順利進入 Recovery 代表此測項為 Pass。

圖 17

TD7.15 Wrong LCRD_X Sequence Test

此測項為 PUT 收到一個錯誤的 LCRD_X 或 LCRD1_X 要進入 Recovery 即為 Pass。圖十八為 Gen1 的 Downstream Port 範例,可從第一個紅框看見 LVS 發送一個 LCRD_D,第二個紅框處 LVS 發送一個錯誤順序的 LCRD_C,最後PUT 在第三個紅框有順利進入 Recovery 代表此測項為 Pass。

圖 18

TD7.16 Link Command Missing Test (Upstream Port Only)

此測項為 PUT 在 tU0RecoveryTimeout 超時前沒有收到 LVS 發送的 LDN,PUT 要進入 Recovery 即為 Pass。

圖十九為 Gen1 的 Upstream Port 範例,從第一個紅框為 tU0RecoveryTimeout 開始點,接著 LVS 都沒有回 LDN,最後在第二個紅框 PUT 進入 Recovery 代表此測項為 Pass。

圖 19

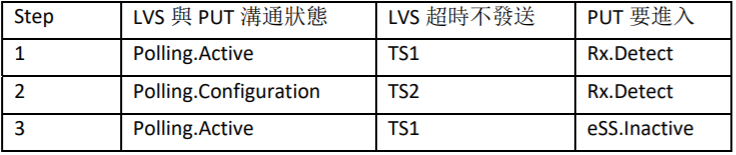

TD7.17 tPortConfiguration Time Timeout Test

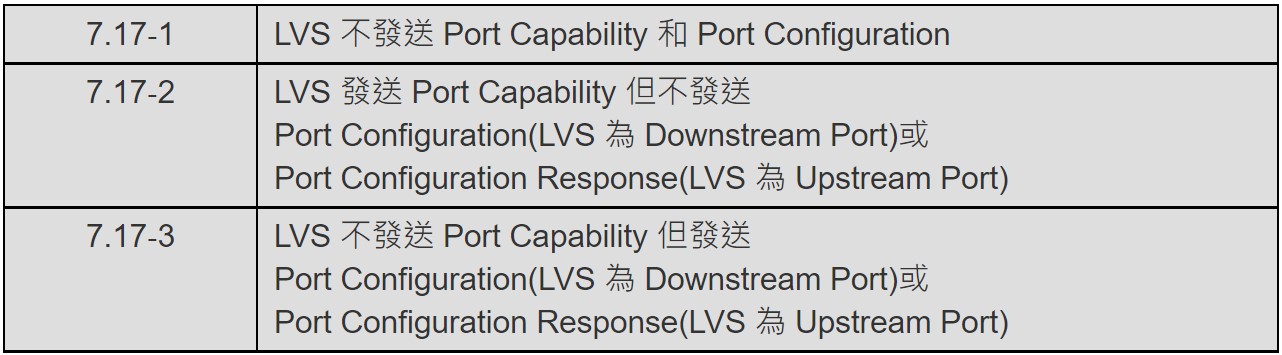

此測項若 PUT 為 Downstream Port 在 tPortConfiguration 超時之後要進入 eSS.Inactive,若 PUT 為 Upstream Port 在 tPortConfiguration 超時之後要進入 eSS.Disabled,規範中 tPortConfiguration 定為 20μs。測試步驟分有三個部分如下表:

表 16

圖二十為 Gen1 的 Downstream Port 測試 TD7.17‐1 範例。第一個紅框可看出 PUT 發出 Port Capability,之後 LVS 完全不發送 LMP 與 PUT 溝通,在第二及第三個紅框可知 PUT 在 25.084μs 之後進入 eSS.Inactive,代表此測試 Pass。

圖 20

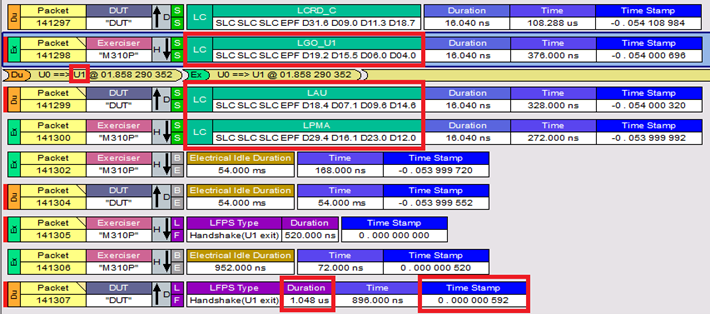

TD7.18 Low Power initiation for U1 Test (Downstream Port Only)

此測項為確保 PUT 能夠進入以及退出 U1 狀態回到 U0 即為 Pass。

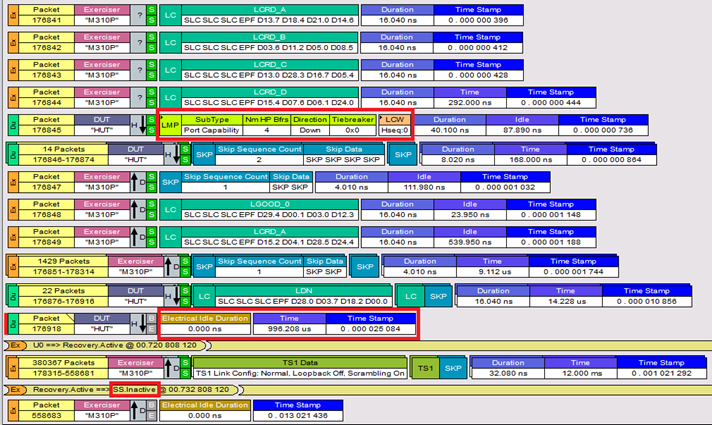

圖二十一為 Gen1 的範例,圖中上到下左到右紅框順序為,PUT 發送 LGO_U1 後,LVS 回送 LAU 且 PUT 再回送 LPMA 進入 U1 狀態,接著 LVS 發送 U1 Exit LFPS 到 PUT 也回送 U1 Exit LFPS 時間要在 300ns〜2μs,PUT 的 U1 Exit LFPS 持續發送時間要在 0.9μs〜1.2μs。

圖 21

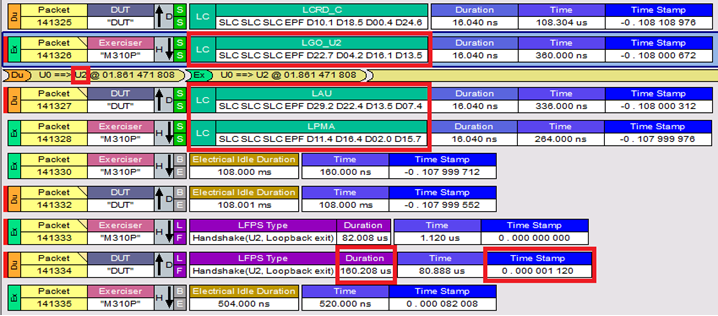

TD7.19 Low Power initiation for U2 Test (Downstream Port Only)

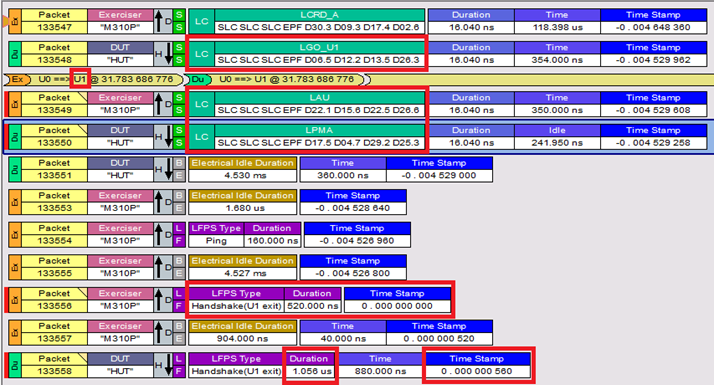

此測項為確保 PUT 能夠進入以及退出 U2 狀態回到 U0 即為 Pass。

圖二十二為 Gen1 的範例,圖中上到下左到右紅框順序為,PUT 發送 LGO_U2 後,LVS 回送 LAU 且 PUT 再回送 LPMA 進入 U2 狀態,接著 LVS 發送 U2 Exit LFPS 到 PUT 也回送 U2 Exit LFPS 時間要在 300ns〜2ms,PUT 的 U2 Exit LFPS 持續發送時間要在 80μs〜2ms。

圖 22

TD7.20 PM_LC_TIMER Deadline Test (Downstream Port Only)

此測項為測試 PUT 在發送 LGO_U1 之後 PM_LC_TIMER 超時前的 tLinkTurnAround 之內收到 LVS 的 LAU 時,PUT 還能夠順利回 LPMA 即為 Pass,請參考下圖範例。

圖 23

TD7.21 PM_LC_TIMER Timeout Test (Downstream Port Only)

此測項為測試 PUT 在發送 LGO_U1 後 PM_LC_TIMER 超時,LVS 不回送 LAU 給 PUT,PUT 要能夠順利進入 Recovery 即為 Pass。圖二十四為範例。

圖 24

TD7.22 PM_ENTRY_TIMER Timeout Test (Upstream Port Only)

此測項為測試 PUT 在 PM_ENTRY_TIMER 超時後,PUT 一樣可以維持在低功耗狀態即為 Pass。

圖二十五為範例,可看見紅框中 LVS 發送 LGO_U1,PUT 回送 LAU 之後,LVS 不回送 LPMA 給 PUT,但 PUT 仍然進入 U1 狀態。

圖 25

TD7.23 Accepted Power Management Transaction for U1 Test (Upstream Port Only)

此測項為 PUT 收到 LGO_U1 要進入 U1,且在規範時間內的 U1 Exit LFPS 溝通能夠 Recovery 回到 U0 即為 Pass。

圖二十六為範例,LVS 發送 LGO_U1,PUT 順利進入 U1,LVS 到 PUT 的 U1 Exit LFPS 要在 300ns〜2μs,PUT 的 U1 Exit LFPS 持續發送時間要在 0.9μs〜1.2μs。

圖 26

TD7.24 Accepted Power Management Transaction for U2 Test (Upstream Port Only)

此測項為 PUT 收到 LGO_U2 要進入 U2,且在規範時間內的 U2 Exit LFPS 溝通能夠 Recovery 回到 U0 即為 Pass。

圖二十七為範例,LVS 發送 LGO_U2,PUT 順利進入 U2,LVS 到 PUT 的 U2 Exit LFPS 要在 300ns〜2ms,PUT 的 U2 Exit LFPS 持續發送時間要在 80μs〜2ms。

圖 27

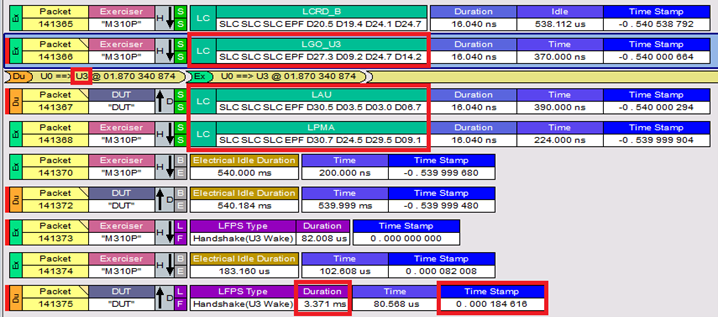

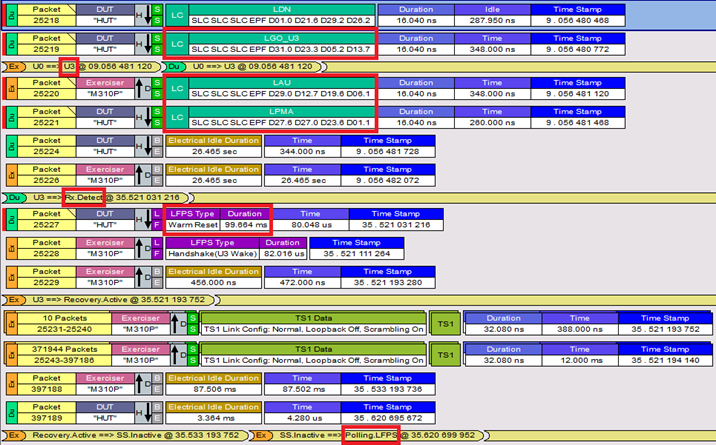

TD7.25 Accepted Power Management Transaction for U3 Test (Upstream Port Only)

此測項為 PUT 收到 LGO_U3 要進入 U3,且在規範時間內的 U3 Exit LFPS 溝通能夠 Recovery 回到 U0 即為 Pass。

圖二十八為範例,LVS 發送 LGO_U3,PUT 順利進入 U3,LVS 到 PUT 的 U3 Exit LFPS 要在 300ns〜10ms,PUT 的 U3 Exit LFPS 持續發送時間要在 80μs〜10ms。

圖 28

TD7.26 Transition to U0 from Recovery Test

此測項要確保 PUT 在 Recovery 狀態時候能夠回到 U0 即為 Pass。

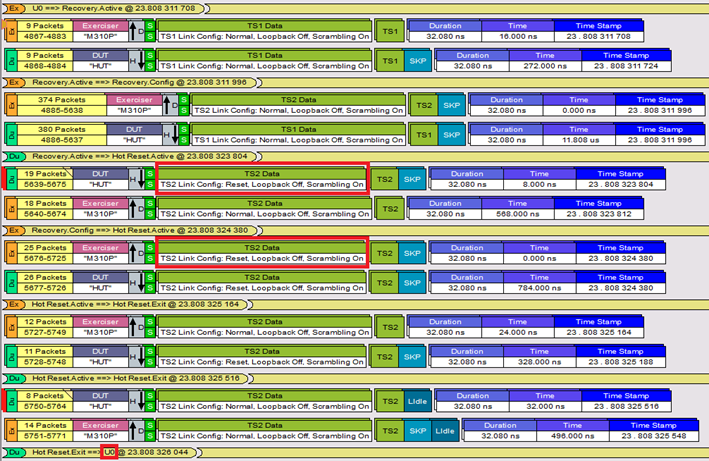

圖二十九為 Gen1 的範例,可從圖中得知一開始在 U0 狀態,LVS 不發送 LGOOD 與 PUT 溝通,使 PENDING_HP_TIMER 超時,所以有在第二個紅框進入 Recovery。接著 PUT 與 LVS 要從 TS1 依照規範訓練回到 U0。

圖 29

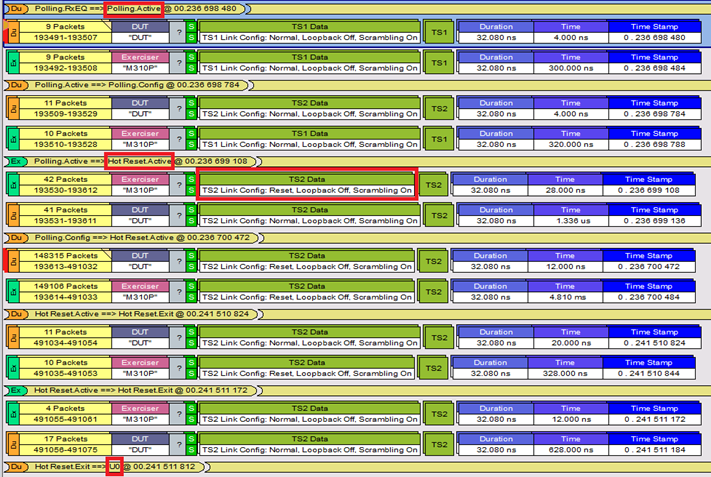

TD7.27 Hot Reset Detection in Polling Test (Upstream Port Only)

PUT 在 Polling 狀態時要能順利偵測到 Hot Reset 即為 Pass。

圖三十為 Gen1 的範例,紅框中可得知在 Polling.Active 狀態,LVS 在收到 PUT 的 TS2 之後,發送含有 Reset bit 的 TS2,PUT 收到後也回送 16 個含有 Resetbit 的 TS2,接著 LVS 再發送連續 4 個不含 Reset bit 的 TS2,最後溝通進入 U0 且要維持 50ms。

圖 30

TD7.28 Hot Reset Detection in U0 Test (Upstream Port Only)

此測項要測試 PUT 在 U0 能順利偵測到 Hot Reset 且不做 Port Configuration 溝通即為 Pass。

圖三十一為 Gen1 的範例,從圖中紅框上到下可知在 U0 時,LVS 發送 TS1 使狀態進入 Recovery,接著 LVS 收到 PUT 的 TS1 之後開始發送含有 Reset bit 的 TS2,然後 PUT 回傳 16 個含有 Reset bit 的 TS2,最後 LVS 發送連續 4 個不含 Reset bit 的 TS2 並進入 U0 維持 50ms。

圖 31

TD7.29 Hot Reset Initiation in U0 Test (Downstream Port Only)

測試 PUT 在 U0 收到 Hot Reset 能夠再訓練回 U0 並維持 50ms 即為 Pass。

圖三十二為 Gen1 的範例,從圖中紅框知 PUT 發送 16 個含有 Reset bit 的 TS2 之後,LVS 也會回傳含有 Reset bit 的 TS2,接著在連續發送 2 個不含 Reset bit 的 TS2,最後訓練進入 U0 並維持 50ms。

圖 32

TD7.30 Recovery on three consecutive failed RX Header Packets Test

測試 PUT 在收到連續 3 個無效的 Header Packets 要進入 Recovery 即為 Pass。

圖三十三為 Gen1 的範例,圖中前三個紅框為 LVS 發送三次含有無效 CRC‐5 的 Header Packet,PUT 在前兩次收到無效的 Header Packet 會回送 LBAD,LVS 會回傳 LRTY 重新發送一次,第三次 LVS 發送無效 Header Packet 時,PUT 會使狀態進入 Recovery,最後重新訓練進 U0 維持 50ms 代表 Pass。

圖 33

TD7.31 Hot Reset Failure Test (Downstream Port Only)

測試 PUT 在做 Hot Reset 失敗時,會做 Warm Reset 即為 Pass。

圖三十四為 Gen1 的範例,圖中可看見第一個紅框 PUT 利用 USB30CV 發送 TS1 準備進入 Recovery,LVS 不回應 PUT,在第二個紅框可看見 PUT 進入 Rx.Detect 發送 Warm Reset LFPS。最後就重新從 Polling.LFPS 溝通進入 U0 維持 50ms。

圖 34

TD7.32 Warm Reset Rx.Detect Timeout Test (Hub Downstream Port Only)

此測項已在 Link Layer 測試中被刪除,在 TD10.109 已包含此測試內容。

TD7.33 Exit Compliance Mode Test (Upstream Port Only)

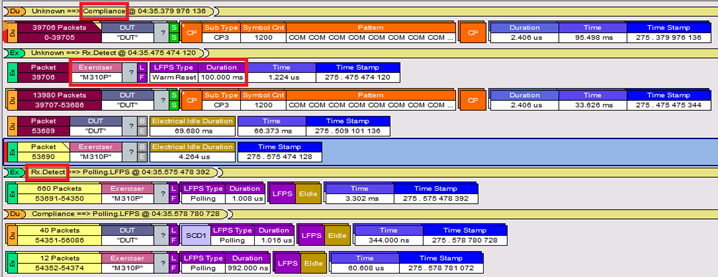

測試 PUT 在 Compliance Mode 收到 Warm Reset LFPS 能離開 Compliance Mode 即為 Pass。

圖三十五為 Gen2 的範例,第一個紅框代表 PUT 在 Compliance Mode,第二個紅框 LVS 發送 Warm Reset LFPS 並進入 Rx.Detect 重新回到 Polling.LFPS 開始訓練。最後訓練進入 U0 並維持 50ms 代表 Pass。

圖 35

TD7.34 Exit Compliance Mode Test (Downstream Port Only)

測試 PUT 在 Compliance Mode 發送 Warm Reset LFPS 能離開 Compliance Mode 即為 Pass。

圖三十六為 Gen1 的範例,第一個紅框代表 PUT 在 Compliance Mode,第二個紅框 PUT 利用 USB30CV 發送 Warm Reset LFPS 並進入 Rx.Detect 重新回到 Polling.LFPS 開始訓練。最後訓練進入 U0 並維持 50ms 代表 Pass。

圖 36

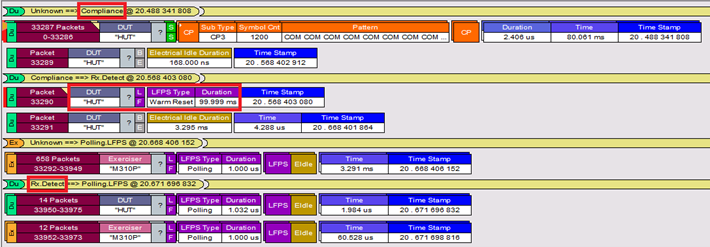

TD7.35 Exit U3 by Reset Test (Downstream Port Only)

測試 PUT 在 U3 發送 Warm Reset LFPS 能離開 U3 即為 Pass。

圖三十七為 Gen1 的範例,從紅框上到下順序,首先 PUT 利用 USB30CV 發送 LGO_U3,接著 LVS 回送 LAU 及 PUT 回傳 LPMA 進入 U3,之後再利用 USB30CV 使 PUT 發送 Warm Reset LFPS 並進入 Rx.Detect 重新回到 Polling.LFPS 開始訓練。最後訓練進入 U0 並維持 50ms 代表 Pass。

圖 37

TD7.36 Exit U3 Test (Host Downstream Port Only)

測試 PUT 在 U3 發送 U3 Exit LFPS 能離開 U3 即為 Pass,此測項只有 Host Silicon 需要測試。

圖三十八為 Gen1的範例,依紅框順序可知 Host 進入 Sleep 狀態,PUT 發送 LGO_U3,LVS 回送 LAU 及 PUT 的 LPMA 使狀態進入 U3。接著叫醒 Host,PUT 發送 U3 Exit LFPS 並進入 Recovery。最後重新溝通回 U0 並維持 50ms 代表 Pass。

圖 38

TD7.37 Packet Pending Test (Upstream Port Only)

測試 PUT 在 Control Transfer 結束前有釋出 Packet Pending flag 即為 Pass。PP bit = 0 為 Not Pending,PP bit = 1 為Pending。

圖三十九為 Gen1 的範例,在最後一組的 Control Transfer 中 SETUP packet 和 IN stage 中 LVS 發送含有 PP bit 為 1 的封包,接著在 STATUS packet 發送 PP bit 為 0 的封包,然後收到 PUT 的 ACK TP,最後 LVS 發送 LGO_U1,PUT 與 LVS 回送 LAU 與 LPMA 進入 U1 代表 Pass。

圖 39

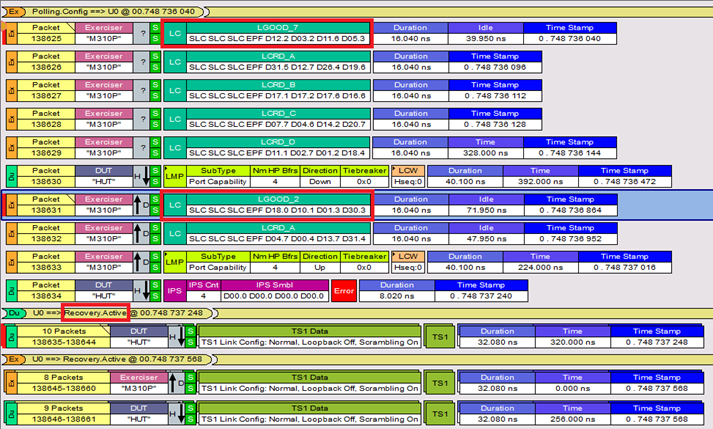

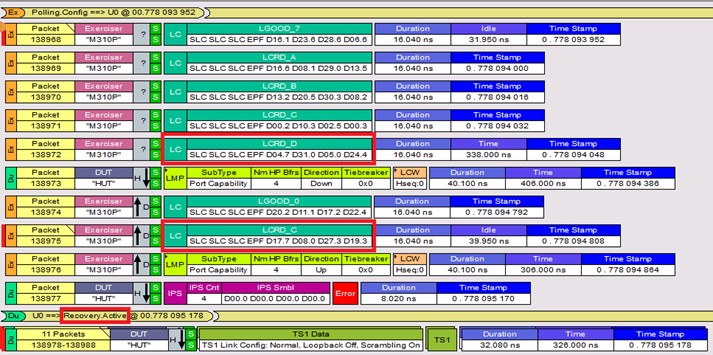

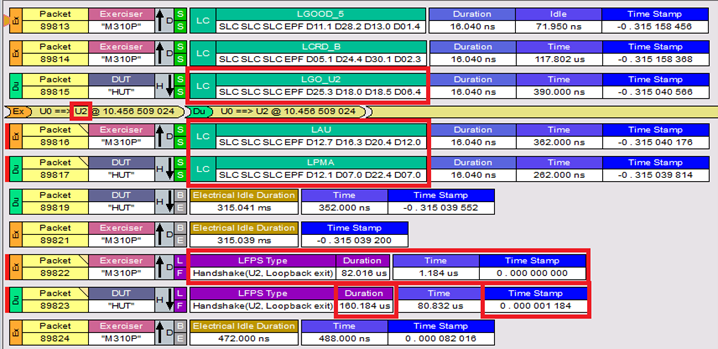

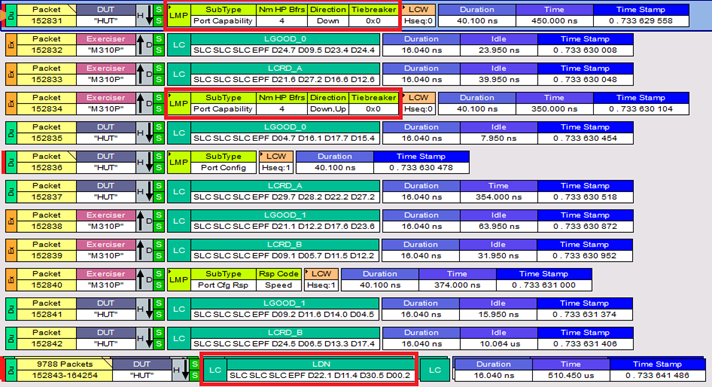

TD7.38 Port Capability Tiebreaker Test

測試 PUT 與 DRD 連接能夠順利溝通進入 U0 維持 50ms 即為 Pass。

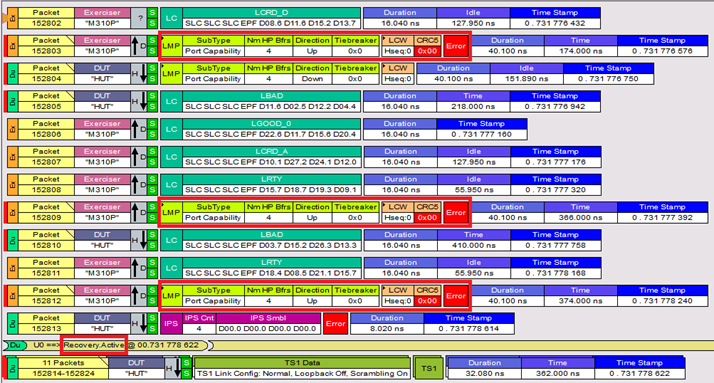

圖四十為 Gen1 的 Downstream Port 範例,依照紅框順序為 PUT 發送 LMP 與 LVS 溝通,LVS 回送一個有 Upstream 和 Downstream Port 兩種能力的 LMP,PUT 仍然順利溝通進入 U0 且要維持 50ms。

圖 40

倘若今天 PUT 是一個 DRD,設 LVS 收到 LMP 的 Tiebreaker 的數值為 X,LVS 每收到一次 Tiebreaker 計數器加 1 次。計數器最多只能到 5 次,超過 5 次即為失敗,溝通狀況整理如下表,最後也是要能夠順利進入 U0 並維持 50ms 為 Pass。

表 17

TD7.39 PortMatch Retry Test (Gen 2 Only)

測試 PUT 在 tPollingActiveTimeout 之後要重新回到 Polling.PortMatch,然後再溝通進入 U0 維持 50ms 即為 Pass。

圖四十一為 Upstream Port 擷取部分測試範例,一開始 PUT 與 LVS 會用 Gen2 溝通進入 Polling.RxEQ 如圖中紅框,LVS 在 tPollingActiveTimeout 超時前都不回 TS1,之後如第二及三個紅框重新回到 Polling.PortMatch 用 Gen1溝通進入 U0 維持 50ms。

圖 41

TD7.40 Polling Retry Test (Downstream Port Only)

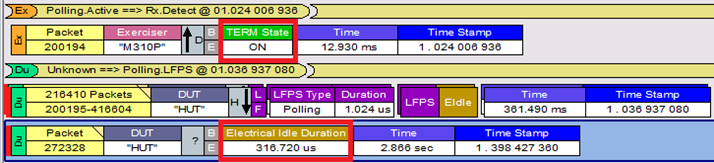

此測項為確保 PUT 在 tPollingLFPSTimeout 之後,前兩次能回到 Rx.Detect 重新從 Polling.LFPS 溝通,第三次超時之後會進入 eSS.Inactive 即為 Pass。

圖四十二為 Gen1 部分範例,LVS 一開始 Termination 起來之後不再發任何訊息,PUT 在第二個紅框進入 Rx.Detect。

圖 42

若今天 PUT 為 Gen1 時,還需繼續多測幾個步驟。首先 LVS 斷開 Termination 200ms 再開啟 Termination,接著測試三個步驟如下表:

表 18

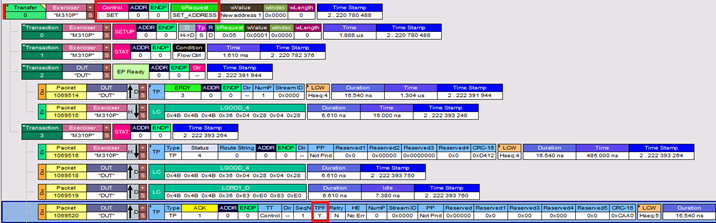

TD7.41 SetAddress TPF Bit Test (Gen 2 Upstream Port Only)

測試 PUT 在 SetAddress Control Transfer 的最後部分有將 TPF bit 設置為 1 即為 Pass。圖四十三為範例,可從圖中最下面的紅框得知 PUT 有將 TPF bit 設置為 1 代表此測試為 Pass。

圖 43

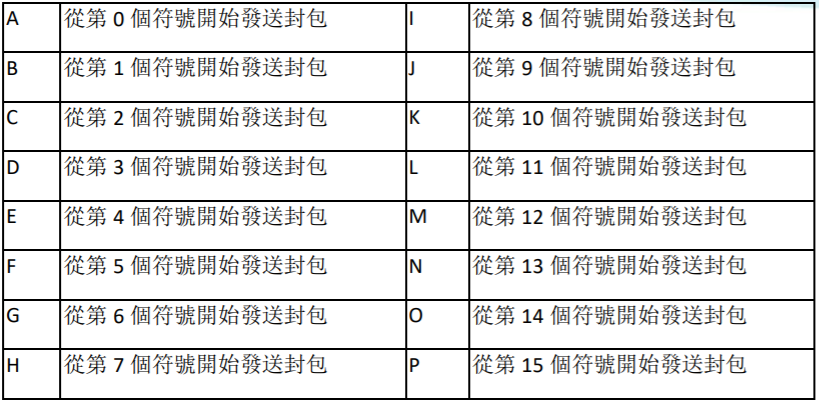

TD7.42 Symbol to Block Alignment Test (Gen 2 Only)

測試 PUT 每次從不同位置的符號開始發送封包皆能夠溝通進入 U0 並維持 50ms 即為 Pass。Gen2 中一個 Block 有 16 個符號加上最前面的 4 個 Block Header 組成。所以測試組合共有 16 組如表二十:

表 19

參考文獻

- Universal Serial Bus 3.2 Specification, September 22, 2017

- Universal Serial Bus 3.1 Link Layer Test Specification, Revision 0.95, February 1, 2019

作者

GRL 台灣技術工程師 曾威華 Wing Tseng

擅長 USB、PCIe、SATA 介面測試。GRL 技術文章作者及講師。希望幫助大家順利測試拿到介面 Logo,彼此互相交流共同成長飛翔。

本文件中規格特性及其說明若有修改恕不另行通知。

發佈日期 2019/06/17 AN-190601-TW